Zero ASIC

Product Categories

About Zero ASIC

Zero ASIC is a privately-held semiconductor device company based in Cambridge, Massachusetts. Zero ASIC is developing the world’s first automated built-to-order System-In-Package design and manufacturing platform targeted at end user applications. Zero ASIC’s breakthrough chiplet approach improves the cost and time of ASIC development by orders of magnitude, removing the barrier to custom silicon for a broad range of energy constrained high performance systems.

Additional Content

ADDITIONAL LINKS

ANALYST REPORTS

- 451 Research Analysts Predicts Accelerators For Future

- Adapteva Believes High-Performance Computing is Ready for an Epiphany

- Adapteva Demos 100Gflops

- Adapteva Included in Gartner Report on Market Trends

- Adapteva: More Flops, Less Watts

- Adapteva’s Epiphany Floating Point Processor Core: A Leading-Edge Lithography May Finally Open Doors

- Epiphany Included in Guide to CPU Cores and Processor IP from Linley Group

- Processors that can do 20 GFLOPS/W

EPIPHANY RESOURCES

PARRALLELLA COMMUNITY FORUM

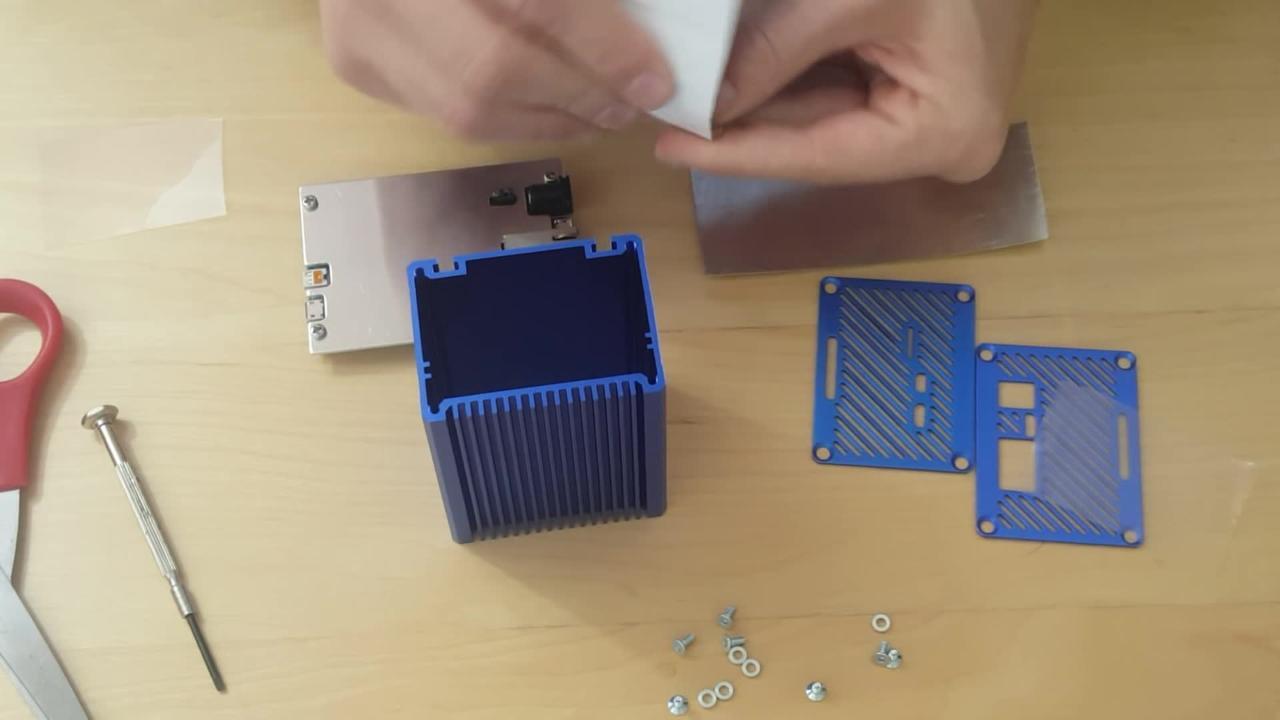

PARRALLELLA RESOURCES

PRODUCT TRAINING PRESENTATIONS

- A 1024-core 70GFLOP/W Floating Point Manycore Microprocessor

- A 1024-core 70GFLOPS/W Floating Point Manycore Microprocessor

- A 25 GFLOP/W Software Programmable Floating Point Accelerator

- A Manycore Coprocessor Architecture for Heterogeneous Computing

- A Scalable Processor Architecture for the Next Generation of Low Power Supercomputer

- A Sub 2 W 64-Core 100 GFLOPS Accelerator Programmable in C/C++ or OpenCL

- An Alternative to GPU Acceleration For Mobile Platforms (Updated) (GF@DAC-2013)

- An Introduction to the Epiphany Manycore Architecture

- Hybrid System Design: The Only Practical Way

- Improving Engineering Efficiency Through Tiled Hierarchical Flows

- Keynote: Kickstarting the Transition to Parallel Computing With Open Hardware

- Keynote: Presenting the Parallella (MIT ARMFEST-2013)

- Keynote: There’s STILL Plenty of Room at the Bottom!

- Parallella: A Love Story

- Peaceful Coexistence Between Architectures

- The Future of HPC: Task-Parallel, Heterogeneous, Efficient, Open

- The Good, the Bad, the Ugly of Semiconductor Crowd Funding