Urychlete návrh systému obrazového rozpoznávání pomocí jednotek MPU řady Renesas RZ/V2

Contributed By DigiKey's North American Editors

2022-09-29

Vzhledem k tomu, že obrazové rozpoznávání na okraji se stává stále důležitější funkcí mnoha produktů, strojové učení (ML) a umělá inteligence (AI) si nacházejí cestu do široké řady aplikačních prostorů. Problém, s nímž se vývojáři potýkají, spočívá v tom, že vidění s podporou ML/AI může vyžadovat větší výpočetní výkon pro spuštění rozpoznávacích algoritmů, než je k dispozici v aplikacích s omezeným výkonem. To také zvyšuje náklady, pokud jsou vyžadována drahá řešení regulace tepla.

Cílem ML/AI na okraji je najít optimální architektonický přístup, který bude vyvažovat výkon a výkon a zároveň poskytne robustní softwarový ekosystém, v rámci kterého bude aplikace vyvíjena.

S ohledem na tyto podmínky tento článek představuje řešení v podobě mikroprocesorové jednotky (MPU) Renesas Electronics řady RZ/V2 s vestavěným hardwarovým akcelerátorem AI. Článek zjišťuje, jakým způsobem může jednotka MPU vyřešit několik problémů, kterým čelí konstruktéři, namísto mikrokontroléru (MCU) nebo špičkové grafické procesorové jednotky (GPU). Popis, jak mohou začít navrhovat systémy obrazového rozpoznávání pomocí řady RZ/V2, je zahrnut spolu s několika „tipy a triky“ pro usnadnění procesu.

Představení jednotek MPU řady RZ/V2

Řada RZ/V2 je řešení otevírající mnoho možností pro vývojáře využívající tříjádrový mikroprocesor. Mikroprocesory řady RZ/V2L obsahují dva procesory Arm Cortex-A55 na frekvenci 1,2 GHz a jádro mikrokontroléru v reálném čase (Arm® Cortex®-M33) na frekvenci 200 MHz. Díly v této řadě navíc obsahují jednotku GPU založenou na multimediálním procesoru Arm Mali-G31 s instrukcemi NEON single instrukce/multiple data (SIMD). Kombinace těchto tří procesorových jader a multimediálního procesoru poskytuje komplexní řešení pro vývojáře pracující na systémech obrazového rozpoznávání.

V současné době existují dvě třídy jednotek MPU v řadě RZ/V2, a sice řada RZ/V2L a RZ/V2M. Řada RZ/V2L používá jednoduchý obrazový signálový procesor (ISP), 3D grafický procesor a vysoce univerzální sadu periferií. Řada RZ/V2M zase přidává vysoce výkonný procesor ISP podporující rozlišení 4K při 30 snímcích za sekundu (fps). Tento článek se zaměřuje na skupinu RZ/V2L obsahující mikroprocesory R9A07G054L23GBG a R9A07G054L24GBG. Hlavní rozdíl mezi těmito dvěma součástkami spočívá ve skutečnosti, že mikroprocesor R9A07G054L23GBG je dodáván v pouzdru 456-LFBGA 15 mm2, zatímco mikroprocesor R9A07G054L24GBG v pouzdru 551-LFBGA 21 mm2.

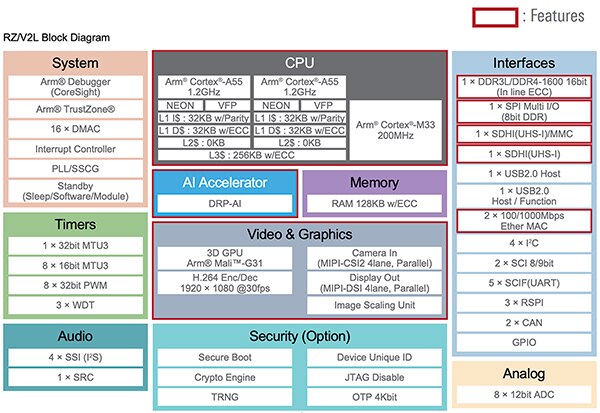

Blokové schéma pro řadu RZ/V2L je na obrázku 1. Kromě tří procesorových jader obsahují jednotky MPU rozhraní pro standardní periferie, jako jsou paměti DDR3/DDR4, SPI, USB, Ethernet, I²C, CAN, SCI, GPIO a analogově-digitální převodník (ADC). Součásti dále zahrnují bezpečnostní funkce, jako je bezpečné spouštění, kryptografický engine a reálný generátor náhodných čísel (TRNG). Řada jednotek MPU se však odlišuje AI akcelerátorem dynamicky rekonfigurovatelných procesorů (DRP).

Obrázek 1: Jednotky MPU řady RZ/V2L podporují různá periferní rozhraní, zabezpečení a možnosti zpracování videa. Kritickým prvkem pro aplikace obrazového rozpoznávání je akcelerátor DRP-AI. (Zdroj obrázku: Renesas Electronics Corporation)

Obrázek 1: Jednotky MPU řady RZ/V2L podporují různá periferní rozhraní, zabezpečení a možnosti zpracování videa. Kritickým prvkem pro aplikace obrazového rozpoznávání je akcelerátor DRP-AI. (Zdroj obrázku: Renesas Electronics Corporation)

Tajná omáčka akcelerátoru DRP-AI

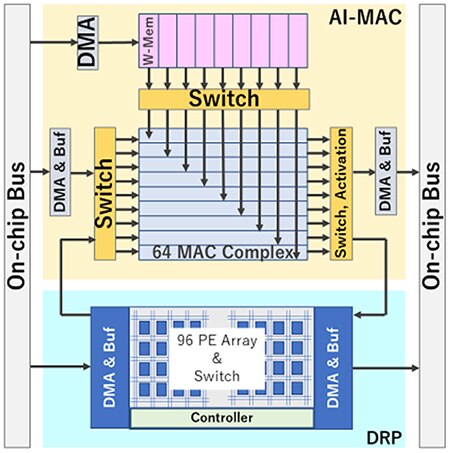

Akcelerátor DRP-AI je tajemstvím, které umožňuje jednotce MPU řady RZ/V2L provádět aplikace obrazového rozpoznávání rychle, s nižší spotřebou energie a nižším tepelným profilem. Akcelerátor DRP-AI se skládá ze dvou součástí: jednotek DRP a AI-multiply-and-accumulate (MAC), které mohou efektivně zpracovávat operace v konvolučních sítích a vše kombinujících vrstvách optimalizací toku dat pomocí interních přepínačů (obrázek 2).

Akcelerátor DRP-AI je určen pro provádění inferencí AI. Akcelerátor DRP-AI využívá jedinečnou dynamickou rekonfigurovatelnou technologii vyvinutou společností Renesas, která poskytuje flexibilitu, vysokorychlostní zpracování a energetickou účinnost. Překladač DRP-AI jako bezplatný softwarový nástroj dále umožňuje uživatelům implementovat optimalizované modely umělé inteligence, které rychle maximalizují výkon. Do externí paměti lze umístit více spustitelných modelů z výstupu překladače DRP-AI. Aplikace pak může během běhu dynamicky přepínat mezi více modely AI.

Jednotka DRP dokáže rychle zpracovat složité činnosti, jako je předzpracování obrazu a vrstvy sdružování modelů AI dynamickou změnou konfigurace hardwaru.

Obrázek 2: Akcelerátor DRP-AI se skládá z jednotek DRP a AI-MAC, které mohou společně efektivně zpracovávat operace v konvolučních sítích a vše kombinujících vrstvách optimalizací datového toku pomocí interních přepínačů. (Zdroj obrázku: Renesas Electronics Corporation)

Obrázek 2: Akcelerátor DRP-AI se skládá z jednotek DRP a AI-MAC, které mohou společně efektivně zpracovávat operace v konvolučních sítích a vše kombinujících vrstvách optimalizací datového toku pomocí interních přepínačů. (Zdroj obrázku: Renesas Electronics Corporation)

Překladač DRP-AI

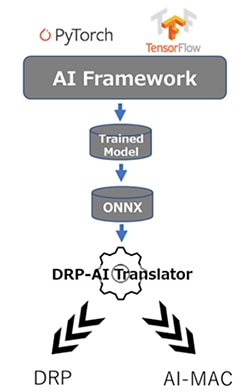

Nástroj překladač DRP-AI generuje spustitelné modely optimalizované pro DRP-AI z trénovaných modelů ONNX, nezávisle na jakémkoli rámci AI. Vývojář by například mohl použít PyTorch, TensorFlow nebo jakýkoli jiný modelovací rámec AI, je-li na jeho výstupu model ONNX. Jakmile je model natrénován, je vložen do překladače DRP-AI, který generuje spustitelné modely DRP a AI-MAC (obrázek 3).

Obrázek 3: Modely AI jsou trénovány pomocí libovolného rámce kompatibilního se systémem ONNX. Model ONNX je pak vložen do překladače DRP-AI , který generuje spustitelné modely DRP a AI-MAC. (Zdroj obrázku: Renesas Electronics Corporation)

Obrázek 3: Modely AI jsou trénovány pomocí libovolného rámce kompatibilního se systémem ONNX. Model ONNX je pak vložen do překladače DRP-AI , který generuje spustitelné modely DRP a AI-MAC. (Zdroj obrázku: Renesas Electronics Corporation)

Překladač DRP-AI má tři hlavní účely:

- Plánování každé operace pro zpracování modelu AI.

- Skrytí režie, jako je doba přístupu do paměti, ke které dochází během každého přechodu operace v plánu.

- Optimalizace struktury síťového grafu.

Překladač DRP-AI automaticky přiděluje každý proces modelu AI jednotkám AI-MAC a DRP, což uživateli umožňuje překladač snadno používat, aniž by byl odborníkem na hardware. Místo toho může vývojář provádět volání prostřednictvím dodaného řadiče a spouštět vysoce výkonný model umělé inteligence. Překladač DRP-AI se navíc může průběžně aktualizovat, aby podporoval nově vyvinuté modely umělé inteligence bez hardwarových změn.

Případy použití systému a procesy

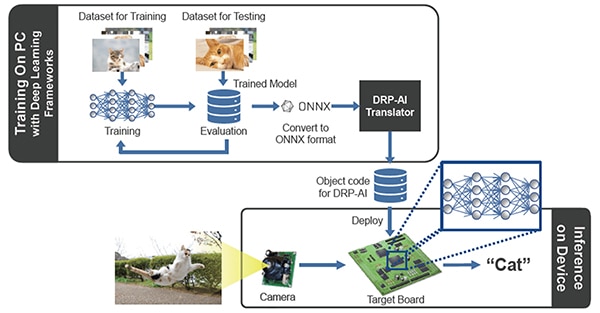

Obecný tok procesu pro využití jednotky RZ/V2L MPU k trénování a nasazení aplikací na obrazové rozpoznávání je znázorněn na obrázku 4. Jako obvykle mohou konstruktéři získat svou datovou sadu a použít ji k trénování modelu obrazového rozpoznávání. Ať už se snaží identifikovat kočky, produkt v nákupním košíku nebo díly, které selžou na montážní lince, proces trénování bude probíhat pomocí známých rámců umělé inteligence. Jakmile je model natrénován, je převeden do formátu ONNX a vložen do překladače DRP-AI, který následně vygeneruje objektový kód spustitelný na hardwaru DRP-AI. Data z kamer, akcelerometrů nebo jiných senzorů jsou pak vzorkována a vložena do spustitelných modelů, což poskytuje výsledek běhu inference.

Obrázek 4: Proces trénování a spuštění algoritmu obrazového rozpoznávání na jednotkách MPU RZ/V2L. (Zdroj obrázku: Renesas Electronics Corporation)

Obrázek 4: Proces trénování a spuštění algoritmu obrazového rozpoznávání na jednotkách MPU RZ/V2L. (Zdroj obrázku: Renesas Electronics Corporation)

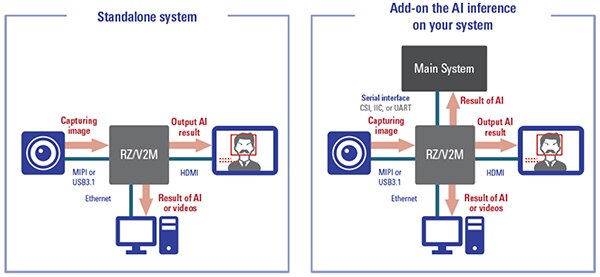

Existuje několik způsobů, jak mohou konstruktéři využít jednotku RZ/V2L MPU ve svých návrzích (obrázek 5). Za prvé, jednotku MPU RZ/V2L lze využívat v samostatných konstrukcích, kde je RZ/V2L jediným procesorem v systému. Díky třem jádrům a hardwaru pro akceleraci AI nemusí být potřeba další výpočetní výkon.

Druhý případ použití je ten, kdy se jednotka RZ/V2L používá jako AI procesor v rozsáhlejším systému. V tomto případě použití jednotka RZ/V2L spustí inferenci AI a vrátí výsledek jinému procesoru nebo systému, který pak na tomto výsledku pracuje. Vybraný případ použití bude záviset na různých faktorech, jako jsou náklady, celková architektura systému, výkon a požadavky na odezvu v reálném čase.

Obrázek 5: Dva případy použití jednotek MPU RZ/V2L zahrnují jejich samostatné použití v aplikaci nebo jako procesor AI v rozsáhlejším systému. (Zdroj obrázku: Renesas Electronics Corporation)

Obrázek 5: Dva případy použití jednotek MPU RZ/V2L zahrnují jejich samostatné použití v aplikaci nebo jako procesor AI v rozsáhlejším systému. (Zdroj obrázku: Renesas Electronics Corporation)

Příklad aplikace v reálné praxi

Existuje mnoho případů použití, kdy lze nasadit technologii obrazového rozpoznávání. Zajímavý příklad je v supermarketu. Zaměstnanec nebo nakupující dnes obvykle při kontrole v obchodě s potravinami skenuje každou položku v košíku. Zajímavým případem použití by bylo detekovat produkty na dopravníku pomocí obrazového rozpoznávání a automaticky je účtovat.

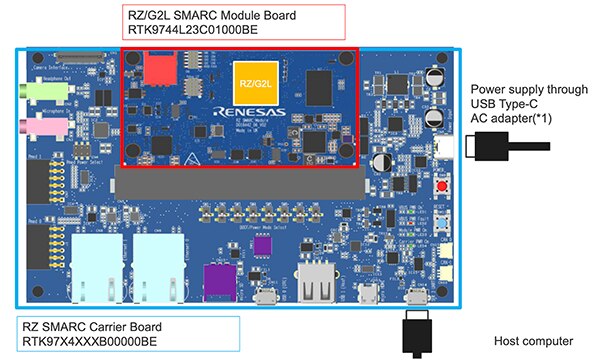

Prototyp by mohl být postaven pomocí jednoduché CMOS kamery a vyhodnocovací desky RTK9754L23S01000BE od společnosti Renesas (obrázek 6). Vestavěná vývojová deska RZ/V2L používá systém na modulu (SOM) a nosnou desku, která umožňuje vývojářům rychle začít pracovat. Vývojová deska navíc podporuje systém Linux společně s různými nástroji, například s překladačem DRP-AI.

Obrázek 6: Vestavěná vývojová deska RZ/V2L je osazena modulem SOM a nosnou deskou, která umožňuje vývojářům rychle uvedení do provozu. (Zdroj obrázku: Renesas Electronics Corporation)

Obrázek 6: Vestavěná vývojová deska RZ/V2L je osazena modulem SOM a nosnou deskou, která umožňuje vývojářům rychle uvedení do provozu. (Zdroj obrázku: Renesas Electronics Corporation)

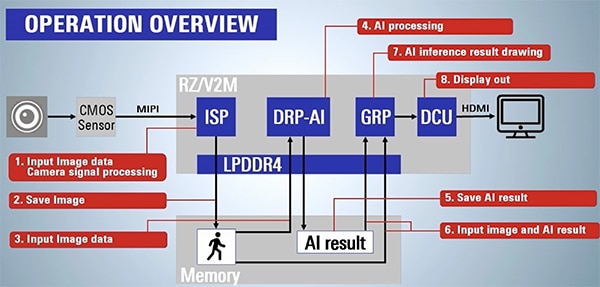

Pracovní přehled komponent potřebných k získávání obrazových dat a vytvoření výsledku AI je znázorněn na obrázku 7. V tomto příkladu aplikace jsou snímky dopravního pásu pořizovány pomocí snímače CMOS prostřednictvím integrovaného procesoru ISP. Poté je snímek uložen do paměti a vložen do enginu DRP-AI. Nakonec DRP-AI engine spustí inferenci a poskytne výsledek AI. Výsledkem může být například nález banánu, jablka nebo jiného ovoce.

Výsledek je často doprovázen úrovní spolehlivosti 0 až 1. Například spolehlivost 0,90 znamená, že AI si je jistá, že detekovala jablko. Na druhou stranu spolehlivost 0,52 může znamenat, že AI se domnívá, že jde patrně o jablko, ale není si jistá. Není neobvyklé vzít výsledek umělé inteligence a zprůměrovat jej z více vzorků, aby se zvýšila pravděpodobnost správných výsledků.

Obrázek 7: Vestavěná vývojová deska RZ/V2L se používá ke spuštění AI inference, která rozpoznává různé druhy ovoce na dopravním pásu. Obrázek ukazuje kroky nezbytné k získání obrázku a vytvoření výsledku AI. (Zdroj obrázku: Renesas Electronics Corporation)

Obrázek 7: Vestavěná vývojová deska RZ/V2L se používá ke spuštění AI inference, která rozpoznává různé druhy ovoce na dopravním pásu. Obrázek ukazuje kroky nezbytné k získání obrázku a vytvoření výsledku AI. (Zdroj obrázku: Renesas Electronics Corporation)

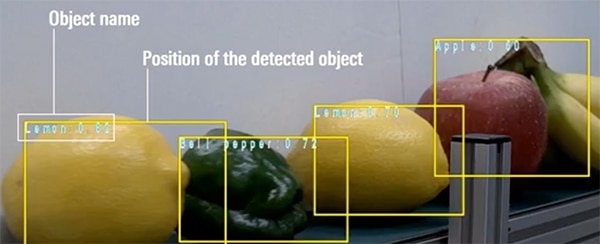

V tomto příkladu se nakonec kolem detekovaného objektu nakreslí rámeček a zobrazí se název rozpoznaného objektu společně s úrovní spolehlivosti (obrázek 8).

Obrázek 8: Příklad výstupu z desky RZ/V2L v aplikaci, která detekuje ovoce a zeleninu na dopravním pásu. (Zdroj obrázku: Renesas Electronics Corporation)

Obrázek 8: Příklad výstupu z desky RZ/V2L v aplikaci, která detekuje ovoce a zeleninu na dopravním pásu. (Zdroj obrázku: Renesas Electronics Corporation)

Tipy a triky pro začínání s deskou RZ/V2L

Vývojáři, kteří chtějí začít se strojovým učením na jednotkách MPU Renesas RZ/V2L, zjistí, že mají spoustu zdrojů, které mohou využít k uvedení do provozu. Zde je několik „tipů a triků“, které by vývojáři měli mít na paměti a které mohou zjednodušit a urychlit jejich vývoj:

- Začněte s vývojovou deskou a existujícími příklady, abyste získali představu o nasazení a spuštění aplikace.

- Pokud je nutné provést více inferencí, uložte spustitelné modely do externí paměti a využijte schopnosti procesoru DRP-AI k rychlému přepínání mezi modely.

- Projděte si dokumentaci a videa na stránkách jednotek RZ/V Embedded AI MPU společnosti Renesas.

- Stáhněte si překladač DRP-AI.

- Stáhněte si balíček podpory RZ/V2L DRP-AI.

Vývojáři, kteří se budou těmito „tipy a triky“ řídit, ušetří poměrně dost času a smutku při začátcích.

Závěr

Jednotky ML a AI si nacházejí cestu do mnoha špičkových aplikací, přičemž schopnost rozpoznávat objekty v reálném čase je stále důležitější. Pro konstruktéry je problém najít správnou architekturu, se lze provádět AI/ML na okraji. Jednotky GPU mají tendenci být energeticky náročné, zatímco jednotky MCU nemusejí mít dostatečný výpočetní výkon.

Bylo ukázáno, že jednotky MPU Renesas řady RZ/V s DRP-AI mají několik výhod, jako je hardwarově akcelerovaná umělá inteligence společně s rozsáhlou podporou nástrojů a prototypování.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.