Maximalizace hustoty výkonu a výkonnosti v aplikacích spínacích převodníků pomocí duálních tranzistorů MOSFET

2024-02-27

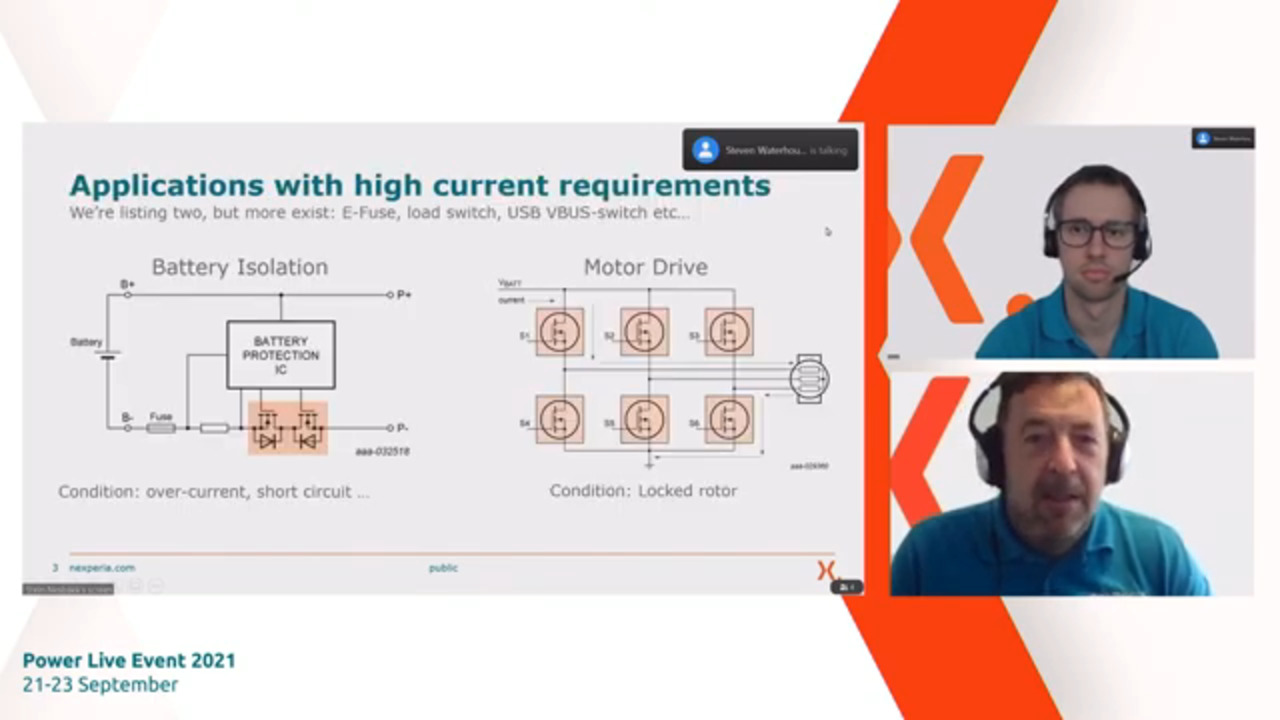

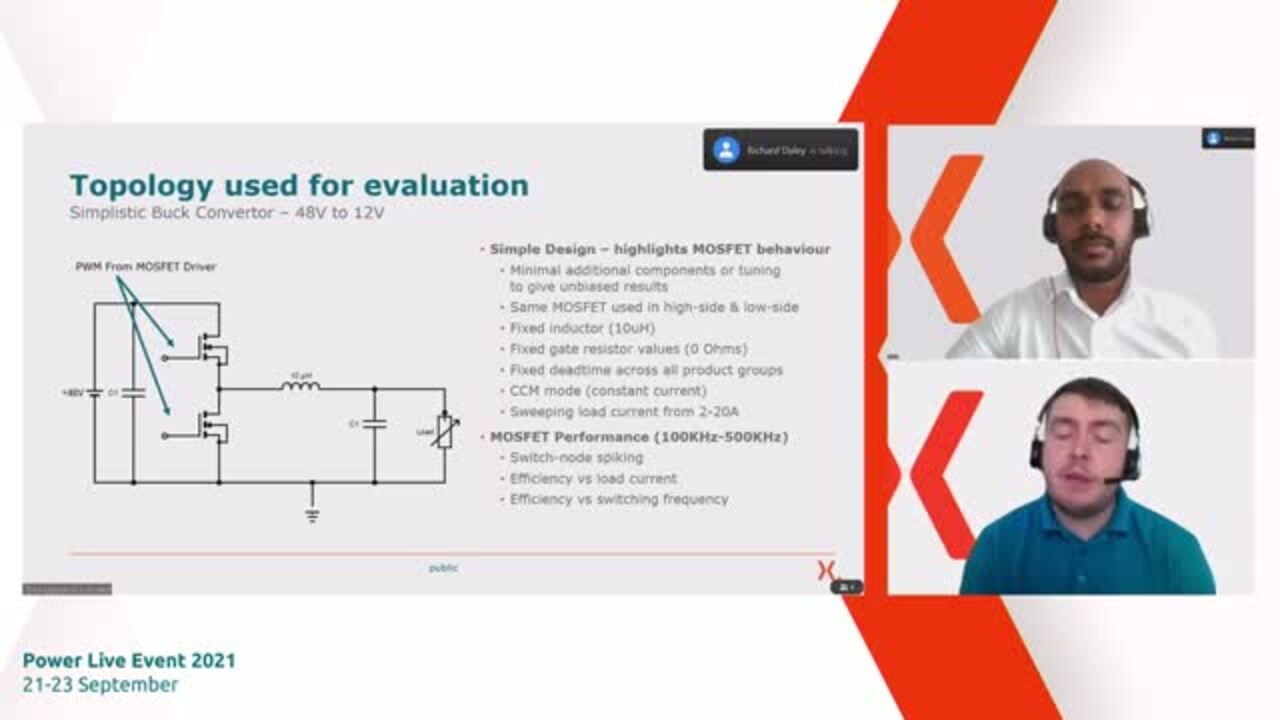

Průmyslové a automobilové spínací převodníky a řadiče motoru vyžadují metaloxidové křemíkové tranzistory řízené elektrickým polem („metal oxide silicon field effect transistor“, MOSFET), které jsou malé, účinné a generují minimální elektrický šum. Tyto požadavky pomáhá splnit duální tranzistor MOSFET.

Při umístění dvou tranzistorů MOSFET do jednoho pouzdra zaberou dva dobře navržené tranzistory MOSFET na desce plošných spojů („printed circuit board“, PCB) méně místa, snižují parazitní indukčnost a lepším tepelným výkonem eliminují potřebu objemných a nákladných chladičů. Taková zařízení mohou spínat bez rušení při několika stovkách kilohertzů, pracují stabilně v širokém teplotním rozsahu a vykazují nízký unikající proud. Konstruktéři však musí rozumět jejich provozním vlastnostem, aby výhod těchto součástek plně využili.

V tomto článku jsou představeny příklady duálních tranzistorů MOSFET od společnosti Nexperia a je zde ukázáno, jak je mohou konstruktéři využít k řešení problémů odolných, vysoce účinných návrhů s omezeným prostorem. Článek pojednává o způsobech optimalizace návrhu obvodů a desek plošných spojů a uvádí tipy pro elektrotepelnou simulaci a analýzu ztrát.

Vyšší účinnost při vysoké rychlosti spínání

Duální tranzistory MOSFET vyhovují mnoha automobilovým (dle normy AEC-Q101) a průmyslovým aplikacím, včetně DC/DC spínacích převodníků, motorových měničů a ovladačů elektromagnetických ventilů. Tyto aplikace mohou používat duální tranzistory MOSFET kromě jiných topologií také ve spínacích párech a polomůstcích.

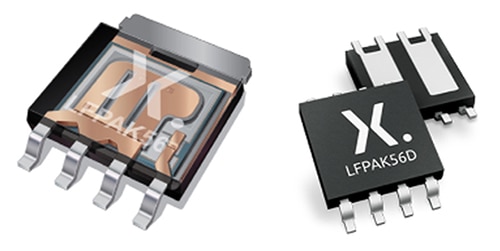

Řada LFPAK56D společnosti Nexperia je pozoruhodným příkladem duálních zařízení MOSFET. Vyznačuje se technologií měděných svorek společnosti Nexperia, které umožňují výjimečnou proudovou kapacitu, nízkou impedanci pouzdra a vysokou spolehlivost (obrázek 1, vpravo). Tyto pevné měděné svorky zlepšují odvod tepla z polovodičového substrátu přes pájené spoje do desky plošných spojů, což umožňuje, aby přibližně 30 % z celkového odebraného tepla proudilo přes piny zdroje. Velké měděné průřezy také snižují ohmické výkonové ztráty a tlumí kmitání snížením indukčnosti parazitního vedení.

Obrázek 1: Pouzdro LFPAK56D (vpravo) má v sobě integrovány dva nezávislé tranzistory MOSFET a využívá struktury měděných svorek podobně jako pouzdro s jedním tranzistorem MOSFET LFPAK56 (vlevo). (Zdroj obrázku: společnost Nexperia)

Obrázek 1: Pouzdro LFPAK56D (vpravo) má v sobě integrovány dva nezávislé tranzistory MOSFET a využívá struktury měděných svorek podobně jako pouzdro s jedním tranzistorem MOSFET LFPAK56 (vlevo). (Zdroj obrázku: společnost Nexperia)

Stejně jako většina součástek určených pro vysokonapěťové spínací převodníky využívá i zařízení LFPAK56D technologii Super Junction. Tato konstrukce snižuje parametry odporu v sepnutém stavu odtok-zdroj („drain-source“) (RDS(on)) a náboje hradlo-odtok („gate-drain“) (QGD), čímž se minimalizují výkonové ztráty. Fungování dvou tranzistorů MOSFET na stejném substrátu dále snižuje odpor odtok-zdroj („drain-source“).

Jako řada tranzistorů MOSFET s technologií Super Junction je řada LFPAK56D odolná vůči lavinovým událostem a má širokou bezpečnou provozní oblast („safe operating area“, SOA). Například všechny ze 100voltových tranzistorů MOSFET v zařízení TrenchMOS PSMN029-100HLX mají 29mΩ RDS(on), zvládnou 68 wattů a mohou propustit až 30 A.

Ke snížení špiček a unikajícího proudu využívá řada LFPAK56D také technologii SchottkyPlus společnosti NXP. Například typický RDS(on) pro model PSMN014-40HLDX je typicky 11,4 mΩ a unikající proud odtok-zdroj („drain-source“) je extrémně nízkých 10 nA.

Pro plné využití vysokých proudů tranzistorů MOSFET musí být deska plošných spojů navržena tak, aby odváděla vysoké teplo a zajišťovala stabilní elektrické spojení. Vysoký tepelný výkon zajišťují vícevrstvé desky plošných spojů s dostatečnými prokovy a velkými, silnými měděnými vodiči.

Zabránění tepelnému lavinovému jevu

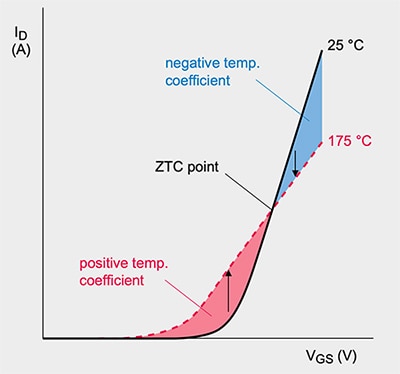

Zatímco plně zapnuté výkonové tranzistory MOSFET jsou tepelně stabilní, při nízkém odtokovém proudu (ID) hrozí tepelný lavinový jev.V tomto provozním stavu má místní ohřev tendenci snižovat prahové napětí hradlo-zdroj („gate-source“) (VGS(th)), což znamená, že se zařízení zapíná snadněji. To vytváří pozitivní zpětnou vazbu, kdy dodatečný proud způsobuje větší zahřívání a ještě nižší VGS(th).

Na obrázku 2 je ukázán tento efekt pro konstantní napětí odtok-zdroj („drain-source“) (VDS). Se zvyšujícím se VGS dochází ke kritickému ID, známému jako nulový teplotní koeficient („Zero Temperature Coefficient“, ZTC). Nad tímto proudem dochází k negativní zpětné vazbě a tepelné stabilitě (modrá oblast). Pod ním dominuje úbytek prahového napětí, což má za následek tepelně nestabilní provozní body, které mohou vést k tepelnému lavinovému jevu (červená oblast).

Obrázek 2: Pod bodem ZTC může tranzistor MOSFET přejít v důsledku tepelně indukovaného úbytku VGS (červená oblast) do tepelného lavinového jevu. (Zdroj obrázku: společnost Nexperia)

Obrázek 2: Pod bodem ZTC může tranzistor MOSFET přejít v důsledku tepelně indukovaného úbytku VGS (červená oblast) do tepelného lavinového jevu. (Zdroj obrázku: společnost Nexperia)

Tento efekt snižuje SOA při nízkých proudech a vysokém napětí odtok-zdroj („drain-source“). Pro rychlé spínací operace se strmým sklonem dV/dt to není významný problém. S tím, jak se doba spínání prodlužuje, např. ke snížení elektromagnetického rušení, se však tepelná nestabilita stává pravděpodobnější a potenciálně nebezpečnější.

Nižší spínací ztráty při vysokých frekvencích

Při výběru tranzistoru MOSFET s technologií Super Junction pro aplikace s rychlým spínáním je nízký QGD zásadní, protože výrazně snižuje spínací ztráty.

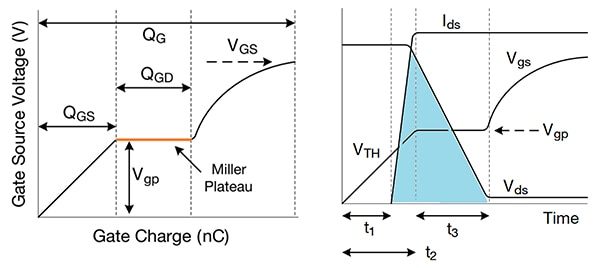

K vysokým ztrátám výkonu dochází během spínání, když se mezi odtokem („drain“), hradlem („gate“) a zdrojem („source“) objeví současně významné změny napětí a proudu. Nízký QGD má za následek krátkou Millerovu rovinu (obrázek 3, vlevo), což vede ke strmému sklonu spínání (dVds/dt) a v konečném důsledku k nižším ztrátám dynamické energie při sepnutí (obrázek 3, modrá oblast vpravo).

Obrázek 3: Krátká Millerova rovina (vlevo) znamená strmý sklon spínání, což má za následek nízké dynamické ztráty (modrá oblast vpravo). Vgp je napětí hradlo-zdroj („gate-source“) Millerovy roviny; VTH je prahové napětí hradla („gate“); IDS je proud odtok-zdroj („drain-source“). (Zdroj obrázku: společnost Vishay)

Obrázek 3: Krátká Millerova rovina (vlevo) znamená strmý sklon spínání, což má za následek nízké dynamické ztráty (modrá oblast vpravo). Vgp je napětí hradlo-zdroj („gate-source“) Millerovy roviny; VTH je prahové napětí hradla („gate“); IDS je proud odtok-zdroj („drain-source“). (Zdroj obrázku: společnost Vishay)

Omezení lavinové energie a ochrana tranzistoru MOSFET

V okamžiku vypnutí statorové cívky v aplikaci motorového pohonu udržuje kolabující magnetické pole tok proudu a generuje vysoké indukční napětí na tranzistoru MOSFET, které se superponuje s napájecím napětím (VDD). Nicméně zpětné průrazné napětí (VBR) diody tělesa tranzistoru MOSFET toto vysoké napětí omezuje. Při takzvaném lavinovém jevu přeměňuje tranzistor MOSFET vystupující magnetickou energii na energii laviny (EDS), dokud proud cívky neklesne na nulu. To může polovodičový krystal rychle přehřát.

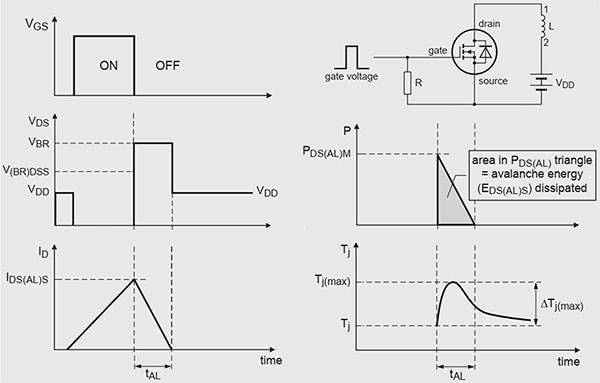

Na obrázku 4 je ukázáno jednoduché ovládání cívky se spínačem MOSFET a časovými signály před, během (časové okno tAL) a po jedné lavinové události. Pokud je množství rozptýlené lavinové energie (EDS(AL)S) příliš vysoké, vzniklé teplo poškodí polovodičovou strukturu.

Obrázek 4: Časovací signály tranzistoru MOSFET před, během (tAL) a po jedné lavinové události. (Zdroj obrázku: společnost Nexperia)

Obrázek 4: Časovací signály tranzistoru MOSFET před, během (tAL) a po jedné lavinové události. (Zdroj obrázku: společnost Nexperia)

Tranzistory MOSFET LFPAK56D jsou navrženy tak, aby byly velmi robustní a podle laboratorních testů společnosti Nexperia vydržely několik miliard lavinových událostí bez poškození. Vzhledem k maximální lavinové energii mohou stupně řadiče cívky upustit od dalších volnoběžných nebo upínacích diod a využívat pouze lavinový provoz těchto tranzistorů MOSFET.

Elektrotepelná online simulace

Chcete-li zlepšit efektivitu systému, nestačí se spoléhat na jednoduchý faktor výhodnosti („Figure of Merit“, FOM), jako je součin RDS × QGD. Místo toho musí konstruktéři provést přesnější analýzu ztrát, která zohlední ztráty tranzistorů MOSFET, vyplývající z následujících faktorů:

- Vodivost při sepnutí

- Ztráty při sepnutí a vypnutí

- Nabíjení a vybíjení výstupní kapacity

- Kontinuita a spínací ztráty diody tělesa

- Nabíjení a vybíjení kapacity hradla

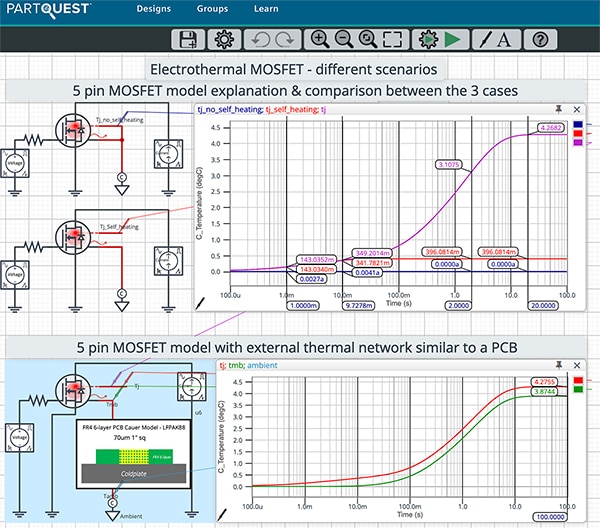

K tomu, aby se minimalizovaly celkové ztráty, musí konstruktéři porozumět vztahu mezi parametry tranzistoru MOSFET a provozním prostředím. Za tímto účelem nabízí společnost Nexperia přesné elektrotepelné modely pro tranzistory MOSFET, které kombinují elektrický a tepelný výkon a reprezentují všechny důležité vlastnosti tranzistoru MOSFET. Vývojáři mohou použít online simulátor PartQuest Explore nebo importovat modely ve formátu SPICE a VHDL-AMS do simulační platformy dle svého výběru.

V době psaní tohoto článku jsou pro tranzistory MOSFET LFPAK56D k dispozici pouze elektrické modely. Proto se následující příklad tepelné simulace zabývá jiným typem tranzistoru MOSFET, modelem BUK7S1R0-40H.

Interaktivní experiment IAN50012 – elektrotepelné modely pro výkonové tranzistory MOSFET simuluje tři scénáře ohřevu pro tranzistor MOSFET BUK7S1R0-40H po sepnutí zatěžovacího proudu 36,25 A. Na obrázku 5 jsou tři nastavení simulace vlevo.

Obrázek 5: Elektrotepelná simulace tranzistoru MOSFET pomocí online simulátoru PartQuest Explore. (Zdroj obrázku: společnost Nexperia)

Obrázek 5: Elektrotepelná simulace tranzistoru MOSFET pomocí online simulátoru PartQuest Explore. (Zdroj obrázku: společnost Nexperia)

V horním případě „tj_no_self_heating“ jsou spoj a montážní základna přímo spojeny s okolní teplotou (Tamb) 0 °C bez tepelného odporu (Rth). V prostředním případě „tj_self_heating“ je čip připojen přes Rth-j a Tj stoupne asi o 0,4 °C. Spodní případ ukazuje montážní základnu (mb) spojenou s okolní teplotou přes Rth_mb šestivrstvé desky FR4 s chladičem. Tmb (zelená) stoupne na 3,9 °C a Tj (červená) stoupne na 4,3 °C.

Závěr

Ultranízkoztrátové tranzistory MOSFET LFPAK56D poskytují vynikající účinnost a hustotu výkonu v rychle spínacích převodnících nebo řadičích motoru. Zde pojednávané aspekty tepelné návrhu obvodu a desky plošných spojů a elektrotepelná simulace ilustrují, jak mohou konstruktéři překonat problémy robustních, vysoce účinných návrhů s omezeným prostorem.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.