Proč a jak používat Efinix FPGA pro zobrazování AI/ML – Část 2: Snímání a zpracování obrazu

Contributed By DigiKey's European Editors

2023-05-05

Poznámka editora: Nové přístupy k architekturám FPGA přinášejí jemnější ovládání a větší flexibilitu pro potřeby strojového učení (ML) i umělé inteligence (AI). 1. část této dvoudílné série představuje jednu takovou architekturu od společnosti Efinix a vysvětlí, jak ji začít používat pomocí vývojové desky. 2. část pojednává o propojení vývojové desky s externími zařízeními a periferiemi, jako je kamera, a o tom, jak využít FPGA k odstranění problémových míst při zpracování obrazu.

FPGA hrají klíčovou roli v mnoha aplikacích, od průmyslového řízení a bezpečnosti až po robotiku či letecký a automobilový průmysl. Díky flexibilní povaze programovatelného logického jádra a širokým možnostem rozhraní je jedním ze stále častějších případů použití FPGA zpracování obrazu, když se dá nasadit strojové učení (ML). FPGA jsou ideální pro implementaci řešení, která mají zásluhou své paralelní logické struktury několik vysokorychlostních kamerových rozhraní. Kromě toho FPGA také umožňuje použití vyhrazených procesních kanálů v logice, čímž eliminuje problémová místa týkající se sdílených prostředků, která by byla spojena s řešeními založenými na CPU nebo GPU.

Tento druhý pohled na FPGA Titanium od společnosti Efinix bude zkoumat referenční aplikaci pro zpracování obrazu, která je dodávána s vývojovou deskou Ti180 M484 architektury FPGA. Cílem je porozumět základním částem návrhu a identifikovat, kde technologie FPGA umožňuje odstranit problémová místa nebo vývojářům nabízí jiné výhody.

Referenční návrh na bázi Ti180 M484

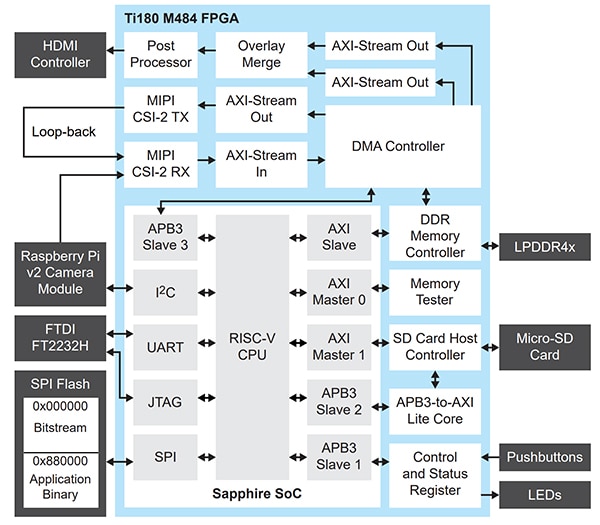

Koncepčně přijímá referenční návrh (obrázek 1) snímky z několika kamer s rozhraním Mobile Industry Processor Interface (MIPI), provádí ukládání snímků do vyrovnávací paměti v LPDDR4x a poté odesílá snímky na displej přes rozhraní High Definition Multimedia Interface (HDMI). Karta FPGA Mezzanine Card (FMC) a čtveřice rozhraní SamtecQSE na desce slouží k zajištění vstupů kamery a výstupu HDMI.

Obrázek 1: Koncepčně přijímá referenční design Ti180 M484 snímky z několika kamer MIPI, ukládá snímky do vyrovnávací paměti v LPDDR4x a poté odesílá snímky na displej přes HDMI. >(Zdroj obrázku: Efinix)

Obrázek 1: Koncepčně přijímá referenční design Ti180 M484 snímky z několika kamer MIPI, ukládá snímky do vyrovnávací paměti v LPDDR4x a poté odesílá snímky na displej přes HDMI. >(Zdroj obrázku: Efinix)

Rozšiřující karta FMC na QSE se používá ve spojení s dceřinou kartou HDMI, která poskytuje cestu k výstupnímu videu, zatímco tři konektory QSE se používají k propojení s kamerami MIPI DFRobotSEN0494. Pokud není k dispozici více kamer MIPI, lze pomocí zpětného smyčkování kanálu jedné kamery simulovat další kamery.

Na první pohled se tato aplikace může zdát jednoduchá. Příjem více toků MIPI s vysokým rozlišením (HD) při vysoké snímkové frekvenci je však náročný. Zde je výhodná technologie FPGA, protože umožňuje návrhářům paralelně využívat více MIPI toků.

Architektura referenčního návrhu využívá s FPGA jak paralelní, tak sekvenční struktury zpracování. Paralelní struktury se používají k implementaci procesních kanálů obrazu, zatímco procesor RISC-V zajišťuje sekvenční zpracování používané pro vyhledávací tabulky FPGA (LUT).

Procesní kanály obrazu lze v mnoha systémech zpracování obrazu na bázi FPGA rozdělit na dva prvky – konkrétně na vstupní a výstupní toky. Vstupní tok je připojen k rozhraní kamery/snímače a funkce zpracování jsou aplikovány na výstup snímače. Tyto funkce mohou zahrnovat Bayerovu konverzi, automatické vyvážení bílé a další vylepšení. Ve výstupním proudu je obraz připraven k zobrazení. To zahrnuje změnu barevných prostorů (např. RGB na YUV) a následné zpracování pro požadovaný výstupní formát, jako je HDMI.

Řetězec pro zpracování vstupního obrazu často pracuje s taktovací frekvencí pixelu snímače. Ta má jiné časování než výstupní řetězec, který se zpracovává na výstupní zobrazovací frekvenci.

Snímková vyrovnávací paměť slouží k připojení vstupu k výstupnímu procesnímu kanálu, které se často ukládá do externí výkonné paměti, jako je LPDDR4x. Tato snímková vyrovnávací paměť odděluje vstupní a výstupní kanály a umožňuje přístup ke snímkové vyrovnávací paměti prostřednictvím přímého přístupu do paměti při příslušné taktovací frekvenci.

Referenční návrh Ti180 používá podobný přístup jako výše uvedené koncepty. Kanál pro zpracování vstupního obrazu implementuje jádro duševního vlastnictví (IP) přijímače MIPI Camera Serial Interface 2 (CSI-2), které je postaveno na vstupu/výstupu (I/O) fyzické vrstvy MIPI (MIPI D-PHY) procesoru Titanium FPGA. MIPI je náročné rozhraní, protože kromě nízkorychlostní a vysokorychlostní komunikace používá jak jednosměrnou, tak diferenciální signalizaci na stejném diferenciálním páru. Integrace MIPI D-PHY do vstupů a výstupů FPGA snižuje složitost návrhu obvodové karty a zároveň zeštíhluje kusovník.

S obrazovým tokem z kamery pak referenční návrh převede výstup MIPI CSI-2 RX na proud AXI (Advanced eXtensible Interface). Proud AXI je jednosměrné vysokorychlostní rozhraní, které zajišťuje proud dat z nadřízeného zařízení do podřízeného. Pro přenos mezi nadřízeným a podřízeným zařízením jsou k dispozici signály handshaking (tvalid a tready) a signály postranního pásma. Tyto signály postranního pásma lze použít k přenosu informací o časování obrazu, jako je začátek snímku a konec řádku.

AXI Stream je ideální pro aplikace zpracování obrazu a umožňuje společnosti Efinix poskytovat řadu IP pro zpracování obrazu, které lze následně snadno integrovat do zpracovatelského řetězce podle požadavků aplikace.

Po přijetí se obrazová data MIPI CSI-2 a časovací signály převedou na AXI Stream a vstupují do modulu přímého přístupu do paměti (DMA), který zapisuje snímek obrazu do LPDDR4x a funguje jako snímková vyrovnávací paměť.

Tento modul DMA pracuje pod řízením jádra RISC-V v FPGA v rámci systému na čipu (SoC) Sapphire. Tento systém SoC poskytuje řízení, jako je zastavování a spouštění zápisů DMA, navíc poskytuje kanálu zápisu DMA potřebné informace pro správný zápis obrazových dat do LPDDR4x. To zahrnuje informace o umístění paměti i šířce a výšce obrazu definované v bajtech.

Výstupní kanál v referenčním návrhu čte obrazové informace z vyrovnávací paměti LPDDR4x pod řízením SoC RISC-V. Data přichází na výstup z DMA IP jako AXI Stream, který se následně převádí z formátu RAW poskytnutého snímačem do formátu RGB (obrázek 2) a připravuje pro výstup přes vestavěný HDMI vysílač ADV7511 od společnosti Analog Devices.

Obrázek 2: Ukázkové obrazy výstupu z referenčního návrhu. (Zdroj obrázku: Adam Taylor)

Obrázek 2: Ukázkové obrazy výstupu z referenčního návrhu. (Zdroj obrázku: Adam Taylor)

Použití DMA také umožňuje čipu Sapphire SoC RISC-V přistupovat ke snímkům uloženým ve snímkové vyrovnávací paměti i k abstraktním statistikám a informacím o snímcích. Sapphire SoC také dokáže zapisovat překryvy do LPDDR4x, takže je lze sloučit s výstupním video proudem.

Moderní obrazové snímače CMOS (CIS) mají několik provozních režimů a lze je nakonfigurovat tak, aby poskytovaly zpracování na čipu, jakož i několik různých výstupních formátů a schémat taktování. Tato konfigurace se obvykle poskytuje přes rozhraní I²C. V referenčním návrhu Efinix tuto komunikaci přes I²C s kamerami MIPI zajišťuje procesor Sapphire SoC RISC-V.

Integrace procesoru RISC-V do FPGA Titanium snižuje celkovou velikost finálního řešení, protože odpadá nutnost implementovat jak složité stavové automaty FPGA, které zvyšují riziko návrhu, tak externí procesory, které rozšiřují kusovník.

Zahrnutí procesoru také umožňuje podporu s další IP pro komunikaci s kartou MicroSD. To umožňuje aplikace v reálném světě, kde může být vyžadováno uložení snímků pro pozdější analýzu.

Celkově je architektura referenčního návrhu Ti180 optimalizována tak, aby umožnila kompaktní, levné, ale přesto velmi výkonné řešení, díky kterému mohou vývojáři snížit náklady na kusovníky prostřednictvím systémové integrace.

Jednou z klíčových výhod referenčních návrhů je, že je lze použít k zahájení vývoje aplikací na vlastním hardwaru, což vývojářům umožňuje převzít kritické prvky návrhu a na jejich základě provést potřebné úpravy. To zahrnuje možnost použít tok TinyML společnosti Efinix k implementaci aplikací TinyML založených na vidění, které běží na FPGA. To může využít jak paralelní povahu logiky FPGA, tak možnost snadno přidávat vlastní instrukce do procesorů RISC-V, což umožňuje vytváření akcelerátorů v rámci logiky FPGA.

Implementace

Jak bylo uvedeno v části 1, architektura Efinix je jedinečná tím, že využívá výměnné logické a směrovací buňky (XLR), které zajišťují jak směrování, tak logické funkce. Video systém, jako je referenční návrh, je smíšený systém, který je náročný jak na logiku, tak na směrování: k implementaci funkcí zpracování obrazu je potřeba rozsáhlá logika a k propojení IP buněk na požadovaných frekvencích je nezbytné rozsáhlé směrování.

Referenční návrh využívá přibližně 42 % XLR buněk v zařízení, což ponechává dostatek prostoru pro doplňky, včetně vlastních aplikací, jako je edge ML.

Využití paměťových bloků RAM a bloků digitálního zpracování signálu (DSP) je rovněž velmi efektivní, neboť využívá pouze 4 z 640 bloků DSP a 40 % paměťových bloků (obrázek 3).

|

Obrázek 3: Alokace zdrojů na architektuře Efinix ukazuje, že je využito pouze 42 % buněk XLR, což ponechává dostatek prostoru pro další procesy. (Zdroj obrázku: Adam Taylor)

Na vstupním/výstupním zařízení se rozhraní DDR pro LPDDR4x používá k poskytování aplikační paměti pro Sapphire SoC a vyrovnávací paměti snímků. Využívají se všechny prostředky MIPI určené pro zařízení a 50 % smyček fázového zámku (obrázek 4).

|

Obrázek 4: Snímek použitých vstupních/výstupních zdrojů a rozhraní. (Zdroj obrázku: Adam Taylor)

Univerzální vstupy/výstupy (GPIO) se používají k zajištění komunikace I²C spolu s několika rozhraními připojenými k SoC Sapphire, včetně NOR FLASH, USB UART a karty SD. HSIO se používá k poskytování vysokorychlostního výstupu videa do HDMI vysílače ADC7511.

Jedním z klíčových prvků při návrhu s FPGA je nejen implementace a přizpůsobení návrhu v FPGA, ale také schopnost umístit logický návrh do FPGA a dosáhnout požadovaného časování při směrování.

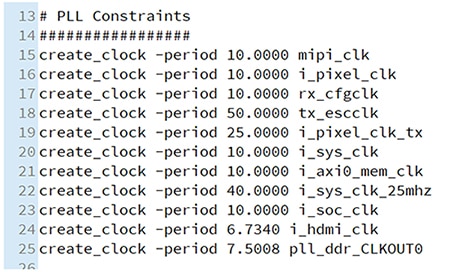

Dávno pryč jsou doby návrhů FPGA s jednou taktovací doménou. V referenčním návrhu Ti180 je několik různých hodin, které běží na vysokých frekvencích. Konečná tabulka časování ukazuje maximální frekvence dosažené pro hodiny v systému. Zde je také vidět požadovaný výkon časování v omezeních (obrázek 5), která mají maximální taktovací frekvenci 148,5 MHz pro výstupní hodiny HDMI.

Obrázek 5: Obrázek omezení hodin pro referenční návrh. (Zdroj obrázku: Adam Taylor)

Obrázek 5: Obrázek omezení hodin pro referenční návrh. (Zdroj obrázku: Adam Taylor)

Implementace časování s ohledem na omezení ukazuje potenciál struktury Titanium FPGA XLR, protože snižuje možné zpoždění směrování, čímž zvyšuje výkon návrhu (obrázek 6).

|

Obrázek 6: Implementace časování s ohledem na omezení ukazuje potenciál struktury Titanium FPGA XLR, protože snižuje možné zpoždění směrování, čímž zvyšuje výkon návrhu. (Zdroj obrázku: Adam Taylor)

Závěr

Referenční návrh Ti180 M484 jasně ukazuje možnosti FPGA Efinix a zejména Ti180. Návrh využívá několik jedinečných struktur vstupu/výstupu k implementaci komplexní cesty zpracování obrazu, která podporuje několik příchozích proudů MIPI. Tento systém zpracování obrazu pracuje pod řízením soft-core SoC Sapphire, který implementuje nezbytné prvky sekvenčního zpracování aplikace.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.