Proč a jak používat Efinix FPGA pro zobrazování AI/ML – Část 1: Začínáme

Contributed By DigiKey's European Editors

2023-04-20

Poznámka editora: Nové přístupy k architekturám FPGA přinášejí jemnější ovládání a větší flexibilitu pro potřeby strojového učení (ML) i umělé inteligence (AI). 1. část této dvoudílné série představuje jednu takovou architekturu od společnosti Efinix a vysvětlí, jak ji začít používat pomocí vývojové desky. 2. část pojednává o propojení vývojové desky s externími zařízeními a periferiemi, jako je kamera.

FPGA hrají klíčovou roli v mnoha aplikacích, od průmyslového řízení a bezpečnosti až po robotiku či letecký a automobilový průmysl. Díky flexibilní povaze programovatelného logického jádra a širokým možnostem rozhraní je jedním ze stále častějších případů použití FPGA zpracování obrazu, když se má nasadit inference ML. FPGA jsou ideální pro implementaci řešení, která mají několik vysokorychlostních kamerových rozhraní. Kromě toho FPGA také umožňuje implementaci vyhrazených procesních kanálů v logice, čímž eliminuje problémová místa, která by byla spojena s řešeními založenými na CPU nebo GPU.

Pro mnoho vývojářů však jejich aplikace vyžadují větší fungování ML/AI a jemnější řízení nebo směrování a logiku, nad rámec toho, co mohou poskytnout klasické architektury FPGA s kombinatorickými logickými bloky (CLB). Tyto problémy řeší novější přístupy k architektuře FPGA. Například architektura Quantum společnosti Efinix využívá blok XLR (eXchangeable Logic and Routing).

Tento článek pojednává o klíčových funkcích a atributech architektury FPGA od společnosti Efinix, zdůrazňuje její schopnosti AI/ML a představuje reálné implementace. Následně probírá vývojovou desku a související nástroje, které mohou vývojáři použít, když chtějí začít s dalším návrhem zobrazování AI/ML.

Zařízení FPGA od společnosti Efinix

Efinix aktuálně nabízí dvě řady zařízení. Původně společnost představila řadu Trion, která nabízí logické hustoty od 4 000 (4K) do 120 000 logických prvků (LE) a je vyrobena pomocí procesu SMIC 40LL. Nejnovější řada zařízení s názvem Titan nabízí logické hustoty od 35 000 do 1 milionu logických prvků a je vyrobena na velmi oblíbeném uzlu TSMC 16 nanometrů (nm).

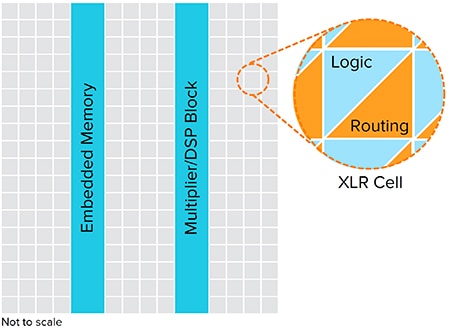

Obě nabídky jsou založeny na architektuře Quantum, která je ve světě FPGA jedinečná. Standardní architektura FPGA je založena na CLB, které na nejjednodušší úrovni obsahují vyhledávací tabulku (LUT) a klopné obvody. CLB implementují logické rovnice, které jsou následně propojeny prostřednictvím směrování. Kvantová architektura společnosti Efinix se díky bloku XLR odklání od samostatných logických a směrovacích bloků.

Blok XLR je jedinečný zejména proto, že ho lze nakonfigurovat tak, aby fungoval jako logická buňka s LUT, registr a sčítač nebo směrovací matice. Tento přístup nabízí jemnější architekturu, která poskytuje flexibilitu směrování a za účelem dosažení požadovaného výkonu podporuje implementace, které jsou náročné na logiku nebo směrování.

Obrázek 1: Blok XLR je jedinečný zejména proto, že ho lze nakonfigurovat tak, aby fungoval buď jako logická buňka s LUT, registr a sčítač, nebo směrovací matice. (Zdroj obrázku: Efinix)

Obrázek 1: Blok XLR je jedinečný zejména proto, že ho lze nakonfigurovat tak, aby fungoval buď jako logická buňka s LUT, registr a sčítač, nebo směrovací matice. (Zdroj obrázku: Efinix)

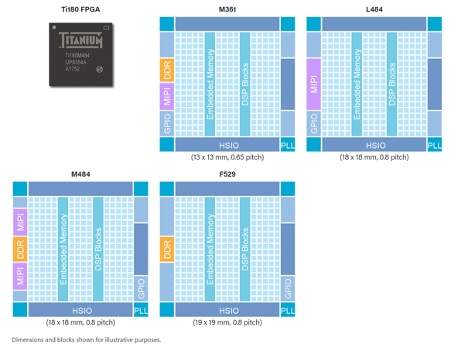

Jakožto nejnovější řada nabízejí zařízení Titanium nejpokročilejší funkce pro vývojáře (Obrázek 2). Spolu s jádrem XLR poskytují multigigabitové sériové linky, které pracují buď rychlostí 16 gigabitů za sekundu (Gb/s), nebo 25,8 Gb/s, v závislosti na zvoleném zařízení. Tato multigigabitová spojení jsou zásadní pro vysokorychlostní přenos dat na čipu i mimo něj.

Obrázek 2: Titanium FPGA Ti180 se dodává v různých variantách v závislosti na šířce sběrnice, vstupech/výstupech a požadavcích na paměť. (Zdroj obrázku: Efinix)

Obrázek 2: Titanium FPGA Ti180 se dodává v různých variantách v závislosti na šířce sběrnice, vstupech/výstupech a požadavcích na paměť. (Zdroj obrázku: Efinix)

Zařízení Titanium také poskytují širokou škálu vstupně-výstupních (I/O) funkcí rozhraní, které lze seskupit jako univerzální I/O (GPIO) a které mohou podporovat standardy I/O s jedním koncem, jako je nízkonapěťový CMOS ( LVCMOS) při 3,3 V, 2,5 V a 1,8 V.

Pro vysokorychlostní a diferenciální rozhraní poskytují zařízení Titanium vysokorychlostní I/O (HSIO), které podporují standardy I/O s jedním koncem, jako je LVCMOS při 1,2 V, 1,5 V a SSTL a HSTL. Diferenciální standardy I/O podporované HSIO zahrnují nízkonapěťovou diferenciální signalizaci (LVDS), diferenciální SSTL a HSTL.

Moderní FPGA také vyžadují úzce propojenou paměť s velkou šířkou pásma, která se používá k ukládání obrazových snímků pro aplikace zpracování obrazu, vzorových dat pro zpracování signálu a samozřejmě k provozu operačních systémů a softwaru pro procesory implementované v FPGA. Řada zařízení Titanium poskytuje možnost propojení s rychlostí DDR4 a nízkoenergetickou DDR4(x) (LPDDR4(x)). V závislosti na přesně vybraném zařízení Titanium je podpora šířky sběrnice x32 (J) nebo x16 (M), zatímco některá zařízení LPDDR4 (L) vůbec nepodporují.

Zařízení FPGA Titanium jsou založena na SRAM a vyžadují konfigurační paměť, přičemž konfiguraci zařízení provádí buď master/slave Serial Peripheral Interconnect (SPI), nebo JTAG. Aby se zajistila bezpečnost této konfigurační metody, používají zařízení FPGA Titanium k zajištění autentizace bitového toku šifrování AES GCM bitového toku spolu s AES GCM a RSA-4096. Silné zabezpečení, jako je toto, je nezbytné, protože FPGA se nasazují na okraji, kde by se mohli pokoušet o přístup a neoprávněnou manipulaci s jejich chováním útočníci s nekalými úmysly.

Představení vývojové desky

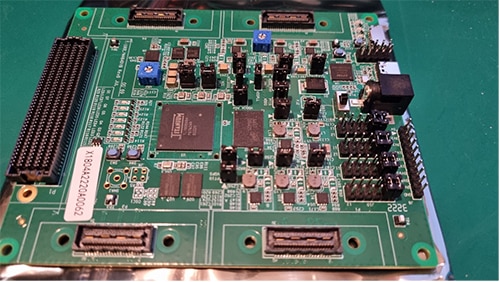

Vývojové desky tvoří kritický prvek procesu hodnocení FPGA, protože pomocí nich lze prozkoumat schopnosti zařízení a prototypové aplikace, čímž pomáhají snižovat celkové riziko. První dostupná vývojová deska pro hodnocení zařízení FPGA Titanium a zahájení prototypování aplikací je Ti180 M484 (Obrázek 3). Deska je vybavena konektorem FPGA Mezzanine Card (FMC) a čtyřmi konektory SamtecQSE.

Obrázek 3: Spolu se zařízení FPGA Titanium obsahuje vývojová sada Ti180 M484 konektor FMC a čtyři konektory Samtec QSE. (Zdroj obrázku: Adam Taylor)

Obrázek 3: Spolu se zařízení FPGA Titanium obsahuje vývojová sada Ti180 M484 konektor FMC a čtyři konektory Samtec QSE. (Zdroj obrázku: Adam Taylor)

FPGA Ti180 osazené na této vývojové desce poskytuje 172K XLR buněk, 32 globálních hodin, 640 prvků digitálního zpracování signálu (DSP) a 13 megabitů (Mb) vestavěné paměti RAM. Prvky DSP poskytují schopnost implementovat násobení 18 × 19 s pevným bodem a 48bitové násobení. Tento DSP se také dá optimalizovat pro operace s jednou instrukcí a více daty (SIMD) běžící v duální nebo čtyřnásobné konfiguraci. Prvky DSP je také možné nakonfigurovat pro provádění operací s pohyblivou řádovou čárkou.

Jako většina vývojových desek, i vývojová deska Ti180 je vybavena jednoduchými LED diodami a tlačítky. Jeho skutečná síla však spočívá ve schopnostech jeho rozhraní. Vývojová deska Ti180 poskytuje konektor FMC s nízkým počtem pinů pro připojení široké škály periferií. Jelikož se jedná o široce používaný standard, existuje mnoho karet FMC, které umožňují vysokorychlostní propojení s analogově-digitálním převodníkem (ADC),digitálně-analogovým převodníkem (DAC), sítí a paměťovými/úložnými řešeními.

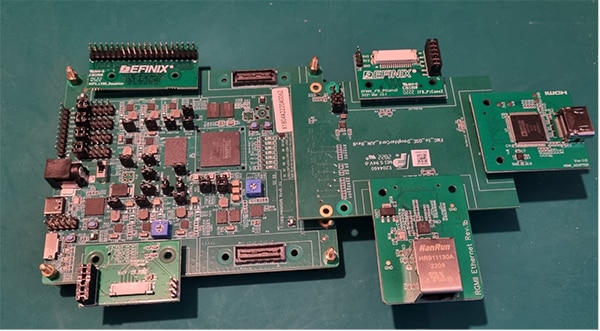

Kromě připojení FMC nabízí deska čtyři konektory Samtec QSE umožňující vývojářům přidat rozšiřující karty. Tyto konektory QSE se používají k poskytování vstupů a výstupů MIPI, přičemž každý konektor QSE poskytuje buď vstup, nebo výstup MIPI.

Obrázek 4: Vývojová sada Ti180 M484 je zobrazena se svou všestrannou řadou možností rozšíření srze konektory QSE a FMC. (Zdroj obrázku: Adam Taylor)

Obrázek 4: Vývojová sada Ti180 M484 je zobrazena se svou všestrannou řadou možností rozšíření srze konektory QSE a FMC. (Zdroj obrázku: Adam Taylor)

Deska Ti180 také poskytuje 256 Mb LPDDR4 pro podporu vysoce výkonné paměti požadované v aplikacích pro zpracování obrazu nebo signálu. Vývojová deska navíc nabízí řadu možností taktování na 25, 33,33, 50 a 74,25 MHz, které lze použít se smyčkou fázového zámku zařízení (PLL) pro generování různých vnitřních frekvencí.

Schopnost přeprogramovat a ladit živě na desce během vývoje je klíčová a vyžaduje připojení JTAG, které poskytuje deska prostřednictvím rozhraní USB-C. K dispozici je také energeticky nezávislá paměť ve formě dvou 256Mb NOR flash zařízení, pomocí kterých lze předvést konfigurační řešení.

Deska se napájí z 12V univerzálního napájecího adaptéru, který je součástí balení. Součástí je také přerušení FMC-to-QSE spolu s rozšiřujícími kartami založenými na QSE pro HDMI, Ethernet, MIPI a LVDS. Pro demonstraci možností zpracování obrazu Ti180 je k dispozici také duální dceřiná karta RPI a dvě karty fotoaparátu IMX477.

Softwarové prostředí

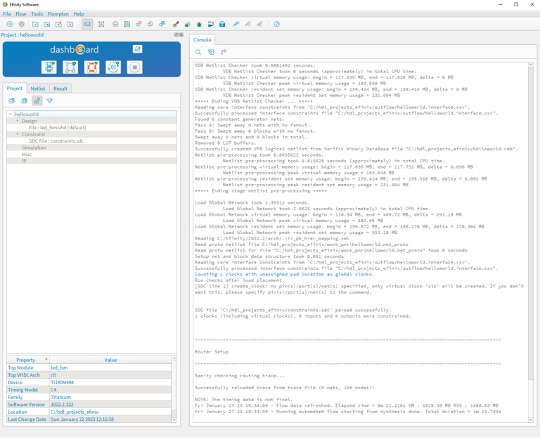

Návrhy implementace zaměřené na vývojovou desku Ti180 využívají software Efinity od společnosti Efinix. Pomocí softwaru lze generovat bitový tok prostřednictvím syntézy a umístění a trasy. Rovněž vývojářům poskytuje bloky duševního vlastnictví (IP), analýzu časování a ladění na čipu.

Pamatujte, že přístup k softwaru Efinity je možný jen s vývojovou deskou. Na rozdíl od jiných dodavatelů však tento nástroj nemá různé verze, které vyžadují další licencování.

V rámci softwaru Efinity se vytváří nové projekty zaměřené na vybrané zařízení. Soubory RTL lze poté přidat do projektu a vytvořit omezení pro načasování a návrh I/O. V softwaru Efinity také vývojáři mohou implementovat návrh I/O s využitím HSIO, GPIO a specializovaných I/O.

Obrázek 5: V rámci softwaru Efinity se vytváří nové projekty zaměřené na vybrané zařízení. (Zdroj obrázku: Adam Taylor)

Obrázek 5: V rámci softwaru Efinity se vytváří nové projekty zaměřené na vybrané zařízení. (Zdroj obrázku: Adam Taylor)

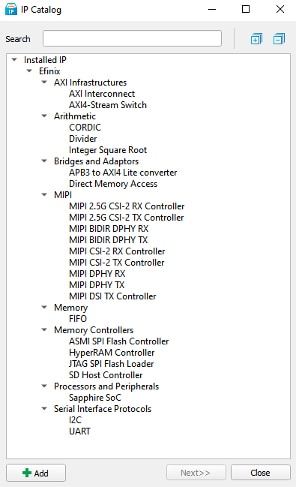

Kritickým prvkem návrhu FPGA je využití IP, zejména pro komplexní IP, jako jsou propojení AXI, řadiče paměti a softcore procesory. Efinity poskytuje vývojářům řadu bloků IP, které lze použít k urychlení procesu návrhu.

Obrázek 6: Software Efinity poskytuje vývojářům katalog IP, který mohou použít k urychlení procesu návrhu. (Zdroj obrázku: Adam Taylor)

Obrázek 6: Software Efinity poskytuje vývojářům katalog IP, který mohou použít k urychlení procesu návrhu. (Zdroj obrázku: Adam Taylor)

Zatímco FPGA jsou vynikající při implementaci struktur paralelního zpracování, mnoho návrhů FPGA obsahuje softcore procesory. Ty umožňují implementaci sekvenčního zpracování, jako je síťová komunikace. Aby bylo možné nasadit softcore procesory v zařízeních Efinix, software Efinity poskytuje konfigurační nástroj SoC (system-on-chip) Sapphire. Pomocí nástroje Sapphire mohou vývojáři definovat víceprocesorový systém, který má mezipaměti i koherenci mezipamětí napříč více procesory, spolu se schopností provozovat vestavěný operační systém Linux. V rámci nástroje Sapphire si vývojář může vybrat mezi jedním a čtyřmi softcore procesory.

Implementovaným softcore procesorem je soft CPU VexRiscV, který je založený na architektuře instrukční sady RISC-V. Procesor VexRiscV je 32bitová implementace, která má rozšíření pro zřetězení a nabízí sadu konfigurovatelných funkcí, takže je ideální pro implementaci v zařízeních Efinix. Volitelné konfigurace zahrnují násobič, atomické instrukce, rozšíření s pohyblivou řádovou čárkou a komprimované instrukce. V závislosti na konfiguraci systému SoC se výkon bude pohybovat mezi 0,86 a 1,05 DMIPS/MHz.

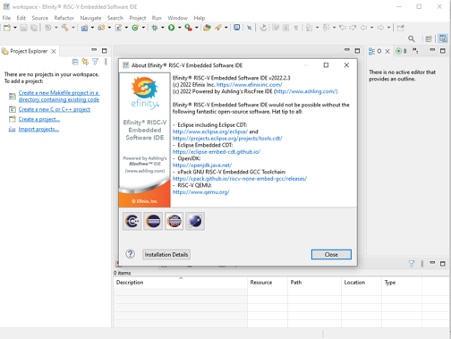

Jakmile je hardwarové prostředí navrženo a implementováno v zařízení Efinix, aplikační software se dá vyvinou pomocí IDE Ashling RiscFree. Ashling RiscFree je IDE založené na Eclipse, které umožňuje vytváření a kompilaci aplikačního softwaru spolu s laděním v cíli pro jemné doladění aplikace před nasazením.

Obrázek 7: Ashling RiscFree je IDE založené na Eclipse, které umožňuje vytváření a kompilaci aplikačního softwaru spolu s laděním v cíli. (Zdroj obrázku: Adam Taylor)

Obrázek 7: Ashling RiscFree je IDE založené na Eclipse, které umožňuje vytváření a kompilaci aplikačního softwaru spolu s laděním v cíli. (Zdroj obrázku: Adam Taylor)

Pokud se vyvíjí vestavěné linuxové řešení, jsou k dispozici všechny nezbytné artefakty spouštění, včetně zavaděče First Stage Boot Loader, OpenSBI, U-Boot a Linuxu pomocí Buildroot. Případně může vývojář použít FreeRTOS, pokud je vyžadováno řešení v reálném čase.

Implementace AI

Implementace AI společnosti Efinix staví na fungování softcore RISC-V. To využívá schopnost vlastních instrukcí procesoru RISC-V k umožnění urychlení řešení TensorFlow Lite. Použití procesoru RISC-V také umožňuje uživatelům vytvářet vlastní instrukce, které lze použít jako součást předzpracování nebo následného zpracování po vyvození AI, což zajišťuje citlivější a determinističtější řešení.

Pokud chcete začít s implementací AI, je prvním krokem prozkoumání modelové zoo společnosti Efinix, což je knihovna modelů AI/ML optimalizovaná pro její koncovou technologii. Vývojáři pracující se zařízeními Efinix mohou do modelové zoo přistupovat a síť trénovat pomocí Jupyter Notebooks nebo Google Colab. Jakmile je trénink sítě dokončen, lze síť převést z modelu s pohyblivou řádovou čárkou na kvantovaný pomocí převodníku TensorFlow Lite.

Jakmile je ve formátu TensorFlow Lite, lze na řešení RISC-V pomocí akcelerátoru tinyML společnosti Efinix vytvořit nasaditelné řešení. Generátor tinyML umožňuje vývojářům přizpůsobit implementaci akcelerátoru a generovat soubory projektu. Při nasazení tímto způsobem se může zrychlení pohybovat mezi 4× a 200× v závislosti na zvolené architektuře a přizpůsobení.

Závěr

Zařízení Efinix poskytují vývojářům flexibilitu díky své jedinečné architektuře XLR. Toolchain poskytuje schopnost nejen implementovat návrh RTL, ale také implementovat komplexní řešení SoC, která nasazují softcore procesory RISC-V. Na softcoru SoC staví řešení AI/ML, které umožňuje nasazení odvození ML.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.