Jak navrhnout a certifikovat funkčně bezpečné systémy založené na RTD

Contributed By DigiKey's North American Editors

2023-07-24

Odporový teplotní detektor (RTD), který se skládá z převodníku a jeho obvodu pro úpravu signálu nízkoúrovňového analogového front-endu (AFE = analog front-end), je široce používaný, přesný a spolehlivý. Pro kriticky důležité a vysoce spolehlivé aplikace je však často nutné navrhnout a zajistit funkčně bezpečný systém prostřednictvím procesu certifikace součástí Route 1S nebo Route 2S.

Certifikace systému pro funkční bezpečnost je složitý proces, protože všechny součásti v systému je nutné zkontrolovat z hlediska možných poruchových režimů a mechanismů. Existují různé metody diagnostiky poruch a používání dílů, které jsou již certifikovány, což tuto pracovní zátěž spolu s certifikačním procesem usnadňuje.

Upozorňujeme, že „spolehlivost“ souvisí s funkční bezpečností, ale není to totéž. Nejjednodušeji řečeno, „spolehlivost“ označuje návrh a implementaci, která funguje podle specifikací bez problémů nebo poruchy, zatímco „funkční bezpečnost“ znamená, že jakékoli poruchy musí být detekovány z návrhu. Pro kriticky důležité aplikace je potřeba spolehlivost i funkční bezpečnost.

Tento článek se bude zabývat základy RTD a jejich obvody pro úpravu signálu v kontextu funkčně bezpečné certifikace. Poté probere různé úrovně certifikace spolehlivosti a poruch a co je nutné k jejich splnění oběma způsoby. Ke znázornění hlavních bodů budou použity dva vícekanálové obvody RTD AFE, pár AD7124 od společnosti Analog Devices, spolu se souvisejícím uspořádáním vyhodnocovací desky.

Úloha funkční bezpečnosti

Úlohou funkční bezpečnosti je dosáhnout osvobození od nepřijatelného rizika zranění nebo poškození zdraví osob prostřednictvím správného provedení jedné nebo více automatických funkcí ochrany/bezpečnosti. Zajišťuje, že produkt, zařízení nebo systém bude i nadále bezpečně fungovat, pokud dojde k poruše. Je zapotřebí v širokém rozsahu průmyslových, komerčních, a dokonce i některých spotřebitelských aplikací, například:

- Autonomní vozidla

- Strojní bezpečnost a robotika

- Průmyslové řídicí systémy (ICS)

- Spotřební produkty pro chytrou domácnost

- Chytré továrny a dodavatelské řetězce

- Bezpečnostní systémy a systémy pro řízení nebezpečných lokalit

Například ve funkčně bezpečném provedení by funkce hlavního vypínače napájení stále podporovala vypnutí napájení, i když by ostatní součásti v systému měly poruchu (obrázek 1).

Obrázek 1: Ve funkčně bezpečném systému nemůže existovat žádná pochybnost nebo nejednoznačnost, že tento spínač bude dělat to, k čemu je navržen. (Zdroj obrázku: společnost Pilla via City Electric Supply Co.)

Obrázek 1: Ve funkčně bezpečném systému nemůže existovat žádná pochybnost nebo nejednoznačnost, že tento spínač bude dělat to, k čemu je navržen. (Zdroj obrázku: společnost Pilla via City Electric Supply Co.)

Základy RTD

Proč se dívat na teplotu a funkční bezpečnost? Jedním z dobrých důvodů je, že teplota je nejčastěji měřeným fyzikálním parametrem. Často se týká bezpečnostních nebo kriticky důležitých aplikací a je podporována širokým výběrem převodníků. Mezi nimi jsou RTD, které jsou koncepčně jednoduché: využívají známý a opakovatelný teplotní koeficient odporu (TCR) kovů, jako jsou nikl, měď a platina. Platinové RTD s odporem 100 ohmů (Ω) a 1000 Ω při 0 °C jsou nejrozšířenější a lze je použít v rozsahu -200 °C až +850 °C.

Tyto RTD mají v tomto teplotním rozsahu vysoce lineární vztah mezi odporem a teplotou. Pro situace vyžadující velmi vysokou přesnost existují korekční a kompenzační tabulky a faktory, které lze použít. Platinový RTD s nominálním odporem 100 Ω (označený jako PT100) má typický odpor 18 Ω při -200 °C a 390,4 Ω při +850 °C.

Použití RTD vyžaduje, aby byl buzen známým proudem, který je obvykle udržován na hodnotě přibližně 1 miliampér (mA), aby se minimalizovalo samovolné zahřívání. V závislosti na jmenovitém odporu RTD se používají i jiné hodnoty proudu.

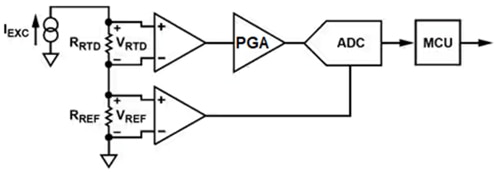

Úbytek napětí na RTD je současně měřen pomocí AFE skládajícího se ze zesilovače s programovatelným ziskem (PGA) a téměř ve všech případech z analogově-digitálního převodníku (ADC) ve spojení s jednotkou mikrokontroléru (MCU) (obrázek 2).

Obrázek 2: Použití RTD k měření teploty vyžaduje vedení známého proudu přes RTD, měření úbytku napětí na něm a poté použití Ohmova zákona. (Zdroj obrázku: společnost Digi-Key)

Obrázek 2: Použití RTD k měření teploty vyžaduje vedení známého proudu přes RTD, měření úbytku napětí na něm a poté použití Ohmova zákona. (Zdroj obrázku: společnost Digi-Key)

Topologie obvodu tohoto základního schématu je totožná s použitím snímacího rezistoru k určení proudu pomocí zátěže, ale zde jsou zaměněny známé a neznámé proměnné. U snímání proudu je odpor znám, zatímco proud je neznámý, takže výpočet je I = V/R. U RTD je proud znám, ale odpor nikoli, takže výpočet je R = V/I.

PGA je třeba k zachování integrity signálu a maximalizaci dynamického rozsahu, protože úrovně napětí na RTD mohou být v rozsahu desítek milivoltů až stovek milivoltů, v závislosti na typu RTD a teplotě.

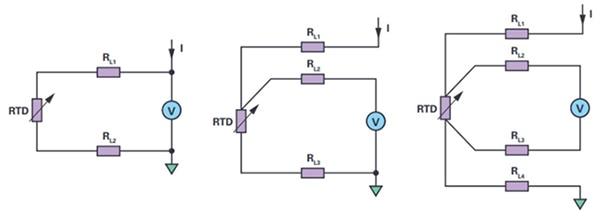

Fyzické spojení mezi zdrojem buzení, RTD a PGA může být rozhraní se dvěma, třemi nebo čtyřmi vodiči. Zatímco dva vodiče jsou v zásadě dostačující, vyskytují se problémy spojené s poklesem IR ve spojovacích vodičích, spolu s dalšími artefakty. Použití topologie se třemi a čtyřmi vodiči v pokročilejším Kelvinově zapojení vede k přesnějšímu a konzistentnějšímu výkonu, i když zvyšuje náklady na kabeláž (obrázek 3).

Obrázek 3: RTD lze řídit a snímat pouze pomocí dvou vodičů (vlevo), ale použití tří vodičů (uprostřed), a dokonce čtyř vodičů (vpravo, Kelvinovo zapojení) umožňuje omezit různé zdroje chyb způsobených vodiči. (Zdroj obrázku: společnost Analog Devices)

Obrázek 3: RTD lze řídit a snímat pouze pomocí dvou vodičů (vlevo), ale použití tří vodičů (uprostřed), a dokonce čtyř vodičů (vpravo, Kelvinovo zapojení) umožňuje omezit různé zdroje chyb způsobených vodiči. (Zdroj obrázku: společnost Analog Devices)

Na začátek něco o terminologii a standardech

Stejně jako v případě mnoha speciálních součástek má funkční bezpečnost mnoho jedinečných termínů, datových sad a zkratek, které jsou široce používány v souvisejících diskuzích. Jsou to následující parametry:

- Selhání v čase (FIT): Počet poruch, které lze očekávat během jedné miliardy (109) hodin provozu zařízení.

- Analýza režimů a účinků poruch (FMEA): Proces kontroly co největšího možného počtu součástí, sestav a subsystémů za účelem identifikace možných poruchových režimů v systému a jejich příčin a účinků.

- Analýza režimů a účinků poruch a diagnostika (FMEDA): Technika systematické analýzy za účelem stanovení četnosti poruch na úrovni subsystému/produktu, poruchových režimů a možnosti diagnostiky.

Pro úplnou analýzu jsou třeba data FIT spolu s analýzou režimů a účinků poruch a diagnostiky (FMEDA) u různých součástí v systému. FMEA nabízí pouze kvalitativní informace, zatímco FMEDA nabízí kvalitativní i kvantitativní informace, což uživatelům umožňuje měřit úroveň závažnosti v souvislosti s poruchovými režimy a seřadit je podle důležitosti. FMEDA přidává riziko, poruchové režimy, analýzu účinků a diagnostiku a informace o spolehlivosti.

- Úroveň integrity bezpečnosti (SIL): Se SIL jsou spojeny čtyři diskrétní úrovně integrity: SIL 1, SIL 2, SIL 3 a SIL 4. Čím vyšší je úroveň SIL, tím vyšší je související úroveň bezpečnosti a tím nižší je pravděpodobnost, že systém nebude správně fungovat.

Hodnocení SIL 2 znamená, že lze diagnostikovat více než 90 % poruch v systému. Aby bylo možné certifikovat návrh, musí návrhář systému certifikačnímu úřadu doložit informace o potenciálních poruchách, ať už se jedná o bezpečné nebo nebezpečné poruchy, a o tom, jak lze poruchy diagnostikovat.

- IEC 61508, s formálním názvem „Funkční bezpečnost elektrických, elektronických a programovatelných elektronických systémů souvisejících s bezpečností“ (a s neformálním názvem pouze „Elektronická funkční bezpečnost“), je specifikací pro funkčně bezpečné návrhy. Dokumentuje postup návrhu potřebný k vývoji dílu s certifikací SIL. Pro každý krok je třeba vytvořit dokumentaci, od konceptu a definice až po návrh, rozvržení, výrobu, sestavení a testování.

Tento proces je známý jako Route 1S a je složitý Existuje však alternativa k procesu Route 1S, která se označuje jako proces Route 2S. Tento proces je „osvědčený při používání“ a je použitelný při navržení velkých objemů produktu do koncových produktů a systémů a ty jsou používány v rámci tisíců hodin akumulovaného provozu.

V rámci procesu Route 2S může být produkt stále certifikován tak, že certifikačnímu úřadu jsou doloženy tyto informace:

- Objemy použité v provozu

- Analýza jakýchkoli vrácení z provozu a podrobnosti o tom, že vrácení nebyla kvůli poruchám v samotné součásti.

- Bezpečnostní listy s podrobnostmi o diagnostice a krytí, které poskytují.

- Pin a matrice – FMEDA

Sloučení rozhraní RTD s procesem SIL Route 2S

Certifikace systému je dlouhý proces, protože všechny součásti v systému musí být zkontrolovány na přítomnost potenciálních poruchových mechanismů, a existují různé metody diagnostiky poruch. Používání dílů, které jsou již certifikované, snižuje vyžadované úsilí a zkracuje certifikační proces.

Vysoce integrovaná a vyspělá součást rozhraní RTD je klíčem k usnadnění certifikace Route 2S, protože definuje úplný balíček řešení, a lze ji tedy zcela charakterizovat daty spojenými s používáním v provozu a s poruchami. To se liší od použití více menších integrovaných obvodů stavebních bloků, kde je nutné analyzovat jejich různá rozhraní a interakce pro konkrétní používanou konfiguraci propojení.

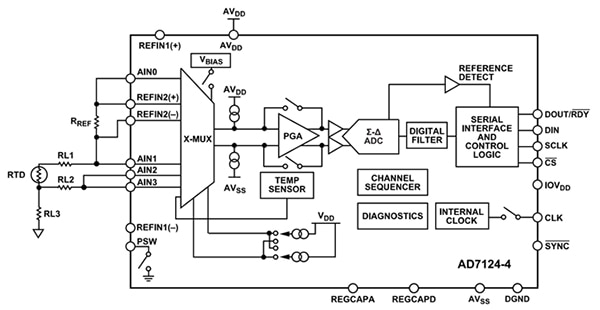

Příkladem je čtyřkanálový AD7124-4 (obrázek 4) a podobný osmikanálový AD7124-8 (dále společně označované jako „AD7124“, když se mluví o jejich mnoha společných funkcích). Tyto součásti se dobře hodí pro proces Route 2S díky vestavěným funkcím samotestování a diagnostiky a také jejich „záznamu výkonu“ v provozu.

Obrázek 4: Čtyřkanálový AD7124-4 je funkčně úplný signálový řetězec RTD ze senzoru do procesoru. (Zdroj obrázku: společnost Analog Devices)

Obrázek 4: Čtyřkanálový AD7124-4 je funkčně úplný signálový řetězec RTD ze senzoru do procesoru. (Zdroj obrázku: společnost Analog Devices)

Tyto integrované obvody jsou kompletním řešením pro vícekanálové měření RTD a obsahují všechny potřebné stavební bloky od senzoru po digitalizovaný výstup a pro komunikaci s přidruženým mikrokontrolérem. Obsahují vícekanálový multiplexer, PGA, 24bitový sigma-delta ADC, zdroje proudu pro RTD, referenční napětí pro interní provoz, systémové hodiny, analogové a digitální filtrování a sériová rozhraní se třemi nebo čtyřmi vodiči pro propojení kompatibilní s SPI, QSPI, MICROWIRE a DSP.

Přítomnost těchto funkcí však ze své podstaty neposkytuje základ pro kvalifikaci SIL Route 2S. Pro funkčně bezpečný návrh je vyžadována řada vestavěných diagnostik pro mnoho funkcí, které tvoří systém RTD. Vícenásobná vestavěná diagnostika v AD7124 minimalizuje složitost i dobu návrhu, a není tedy třeba duplikovat signálový řetězec pro diagnostické pokrytí.

Tyto diagnostiky mimo jiné zahrnují sledování zdroje napájení, referenčního napětí a analogového vstupu; detekci otevřeného vodiče k RTD; kontrolu převodního a kalibračního výkonu; kontrolu funkčnosti signálového řetězce; sledování funkcí čtení/zápisu; a sledování obsahu registru.

Jak se tyto formulace „vysoké úrovně“ promítnou do nezbytné diagnostiky na čipu? Odpověď má mnoho aspektů, včetně těchto:

Diagnostika SPI: Pro každý zápis do AD7124 generuje procesor hodnotu cyklického redundantního součtu (CRC), která je připojena k informacím odesílaným do ADC. ADC poté generuje svou vlastní hodnotu CRC z přijatých informací a porovnává ji s hodnotou CRC přijatou z procesoru. Pokud obě hodnoty souhlasí, informace jsou nedotčené a budou zapsány do příslušného registru na čipu.

Pokud se hodnoty neshodují, znamená to, že při přenosu došlo k malému poškození, a integrovaný obvod nastaví příznak chyby, který udává, že došlo k poškození dat. AD7124 se také sám chrání tím, že nezapisuje poškozené informace do registru.

Podobný postup CRC se používá při čtení informací z AD7124 do systémového procesoru. Rozhraní nakonec také spočítá hodinové impulzy, aby bylo zajištěno, že s každým čteným nebo zapisovaným datovým rámcem se vyskytne pouze osm takových impulsů, čímž je zajištěno, že nedojde k závadě hodin.

Kontroly paměti: CRC se také používá k ověření obsahu registrů při zapnutí nebo při každé změně registrů na čipu (například při změně zesílení). Proces CRC se také pravidelně provádí, aby se zajistilo, že se žádný paměťový bit „nepozměnil“ kvůli šumu nebo jiným důvodům. Pokud dojde ke změně a procesor je následně označen příznakem, že nastavení registrů bylo poškozeno, může resetovat ADC a znovu načíst registry.

Kontroly signálového řetězce: Všechna kriticky důležitá statická napětí lze zkontrolovat prostřednictvím ADC, včetně napájecích lišt, výstupů regulátorů LDO (low-dropout) a referenčních napětí. Lze také zkontrolovat přítomnost nebo nepřítomnost externího kondenzátoru v rámci LDO. Kromě toho lze na vstup ADC použít známé napětí za účelem kontroly ADC a nastavení funkce zesílení. Dále mohou být přes analogové vstupy přivedeny známé proudy za účelem kontroly přerušení nebo zkratu RTD.

Konverze a kalibrace: Výsledky konverze ADC jsou průběžně kontrolovány, aby se zjistilo, zda vyjadřují samé nuly nebo koncovou hodnotu, přičemž obě možnosti znamenají problém. Bitový tok z modulátoru v jádru ADC je sledován, aby se zajistilo, že nedošlo k jeho saturaci, a pokud dojde k saturaci (to znamená, že v modulátoru se vyskytlo 20 po sobě jdoucích jedniček nebo nul), je nastaven příznak chyby.

Frekvence hlavních hodin: Frekvence těchto hodin řídí nejen rychlost konverze, ale také určuje frekvence zádrže digitálních filtrů 50/60 Hertz (Hz). Interní registr v AD7124 umožňuje doprovodnému procesoru časovat, a tím pádem kontrolovat přesnost hlavních hodin.

Další funkce: AD7124 obsahuje snímač teploty, který lze také použít ke sledování teploty matrice. Obě verze mají hodnocení elektrostatického výboje (ESD) 4 kilovolty (kV) pro robustní výkon a obě jsou uloženy v obalu LFCSP o rozměrech 5 × 5 milimetrů (mm), který je vhodný pro jiskrově bezpečné návrhy.

Vzhledem k vnitřní složitosti, propracovanosti a pokročilým funkcím samotestování AD7124-4 a AD7124-8, dává smysl mít k dispozici prostředky, kterými lze integrované obvody zkoušet a vyhodnocovat.

Pro splnění těchto možností nabízí společnost Analog Devices dvojici propojených desek: vyhodnocovací desku EVAL-AD7124-4SDZ pro AD7124-4 (obrázek 5) a doplňkovou desku EVAL-SDP-CB1Z SDP (platforma demonstrace systému)/deska rozhraní (obrázek 6). První uvedená je specifická pro AD7124-4 a funguje společně s druhou, což zajišťuje komunikaci s počítačem uživatele a vyhodnocovacím softwarem přes připojení USB.

Obrázek 5: EVAL-AD7124-4SDZ je vyhodnocovací deska pro regulátor AD7124-4. (Zdroj obrázku: společnost Analog Devices)

Obrázek 5: EVAL-AD7124-4SDZ je vyhodnocovací deska pro regulátor AD7124-4. (Zdroj obrázku: společnost Analog Devices)

Obrázek 6: Deska EVAL-SDP-CB1Z/deska rozhraní je doplňkem vyhodnocovací desky EVAL-AD7124-4SDZ a poskytuje připojení USB k hostitelskému počítači. (Zdroj obrázku: společnost Analog Devices)

Obrázek 6: Deska EVAL-SDP-CB1Z/deska rozhraní je doplňkem vyhodnocovací desky EVAL-AD7124-4SDZ a poskytuje připojení USB k hostitelskému počítači. (Zdroj obrázku: společnost Analog Devices)

Uspořádání vyhodnocení je podporováno softwarem AD7124-4 EVAL+, který plně konfiguruje funkci registru zařízení AD7124-4 a zkouší integrovaný obvod. Poskytuje také analýzu v časové oblasti ve formě grafů průběhu vlny, histogramů a související analýzy šumu pro hodnocení výkonu ADC.

Přechod na funkčně bezpečný návrh

Je důležité si uvědomit, že AD7124-4 a AD7124-8 nemají hodnocení SIL, což znamená, že nejsou navrženy a vyvinuty pomocí vývojových směrnic podle definice standardem IEC 61508. Pochopením koncové aplikace a prostřednictvím vhodného použití různých diagnostik je však možné posoudit jejich použití v návrhu s hodnocením SIL.

Při procesu certifikaci Route 1S je třeba zohlednit více aspektů analýzy a řešení poruch, které mohou být systémové nebo náhodné. Systémové poruchy jsou způsobeny návrhovými nebo výrobními nedostatky, například přerušení šumem kvůli nedostatečnému filtrování na kolíku externího přerušení nebo nedostatečná rezerva pro signál. Oproti tomu náhodné poruchy jsou způsobeny fyzikálními příčinami, například korozí, tepelným namáháním nebo opotřebením.

Důležitým problémem je nebezpečná nezjištěná porucha, které se řeší více technikami. Za účelem minimalizace náhodných poruch používají návrháři jeden nebo všechny tři postupy:

- Spolehlivější součásti, které jsou méně namáhané.

- Diagnostika, která se spoléhá na vestavěné mechanismy detekce implementované prostřednictvím hardwaru nebo softwaru.

- Tolerance vůči poruchám prostřednictvím redundantních obvodů. Přidáním redundantní cesty je možné tolerovat jednu poruchu. Tento systém se nazývá hardwarová poruchová tolerance 1 (HFT 1), což znamená, že jedna porucha nemůže způsobit selhání systému.

Jedním z nástrojů pro pochopení pokrytí úrovně SIL je matice, která vykresluje poměr bezpečných poruch (SFF) (množství diagnostického pokrytí) a tolerance vůči poruchám hardwaru (redundance) (obrázek 7).

|

|||||||||||||||||||||||

Obrázek 7: Tato matice charakterizuje poměr bezpečných poruch (SFF) oproti toleranci vůči chybám hardwaru (HFT) a poskytuje informace o pokrytí SIL. (Zdroj obrázku: společnost Analog Devices)

Řádky uvádějí míru diagnostického pokrytí, zatímco sloupce uvádějí toleranci vůči chybám hardwaru. HFT 0 znamená, že pokud v systému dojde k jedné poruše, dojde ke ztrátě bezpečnostní funkce. Vyšší úroveň diagnostiky snižuje potřebnou míru redundance systému nebo zlepšuje úroveň SIL řešení se stejnou úrovní redundance (pohyb dolů v matici).

Všimněte si, že FMEDA obvyklé teplotní aplikace pomocí těchto zařízení uvádí poměr bezpečných poruch (SFF) vyšší než 90 % podle standardu IEC 61508. K zajištění této úrovně pokrytí prostřednictvím redundance by byly normálně vyžadovány dva tradiční ADC, ale AD4172 vyžaduje pouze jeden ADC, což poskytuje významné úspory nákladů v kusovníku (BOM) a prostoru na desce.

Dokumentace pro návrhy s hodnocením SIL

K dosažení certifikace Route 1S je potřeba rozsáhlá dokumentace. Mezi nezbytné zdrojové dokumenty patří:

- Bezpečnostní list (bezpečnostní příručka pro díl s hodnocením SIL)

- Pin FMEDA a matrice FMEDA s poruchovými režimy, účinky a analýzou obou možností

- Kontrolní seznam v příloze F (definováno standardem IEC 61508)

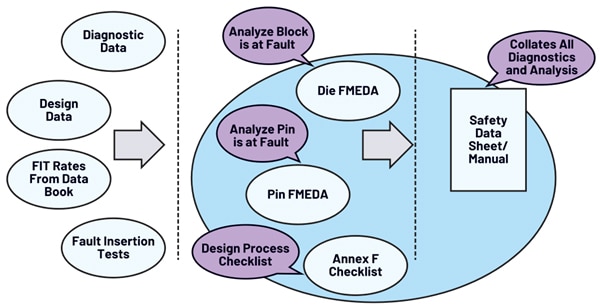

Tato dokumentace pochází z různých zdrojů (obrázek 8):

- Diagnostická data z datového listu zachycují všechny diagnostické funkce dostupné v dílu.

- Návrhová data se vztahují na interní data. Například oblast matrice a vliv každého vnitřního bloku dílu.

- FIT s hodnocením různých součástí je k dispozici v datové knize.

- Testy vkládání poruch se provádějí pro bloky, které nelze analyzovat pomocí návrhových a diagnostických dat. Tyto testy jsou plánovány na základě požadavků aplikace a výsledky testů vkládání poruch se používají k posílení dokumentů FMEDA a FMEA.

Obrázek 8: Různé zdroje dokumentace jsou seskupeny a shromážděny, aby poskytovaly úplný informační balíček potřebný pro certifikaci SIL. (Zdroj obrázku: společnost Analog Devices)

Obrázek 8: Různé zdroje dokumentace jsou seskupeny a shromážděny, aby poskytovaly úplný informační balíček potřebný pro certifikaci SIL. (Zdroj obrázku: společnost Analog Devices)

Podrobnější pohled na konkrétní fakta:

- Bezpečnostní příručka nebo bezpečnostní list používá všechny kompilované informace k zajištění nezbytných požadavků umožňujících integraci AD7124-4 nebo AD7124-8. Shromažďuje všechny diagnostiky a analýzy, které pocházejí z různých dokumentů a datových sad.

- Matrice FMEDA pro AD7124-4 a AD7124-8 analyzuje hlavní bloky ve schématu aplikace, identifikuje režimy a účinky poruch a kontroluje diagnostiku a analýzy pro konkrétní bezpečnostní funkci. Analýza modulu hodin například uvádí poruchové režimy, vliv každého z nich na výstup, míru diagnostického pokrytí a analýzu dopadu (obrázek 9).

|

Obrázek 9: Tato tabulka definuje poruchový režim bloku hlavních hodin, účinky, diagnostiku a analýzu. (Zdroj obrázku: společnost Analog Devices)

Výsledkem této matrice FMEDA je kvantitativní prezentace četnosti poruch pro bezpečné poruchy, nebezpečné zjištěné poruchy a nebezpečné nezjištěné poruchy. To vše se používá k výpočtu SFF.

Pin FDEMA se na poruchy dívá z jiného hlediska. Analyzuje různé typy poruch na pinech AD7124-4 a AD7124-8 a jejich výsledek pro aplikaci RTD. Tuto akci provádí pro každý jednotlivý pin a popisuje výsledek pro případ, kdy se pin otevře, zkratuje proti napájení/uzemnění nebo se zkratuje proti sousedním pinům.

Kontrolní seznam v příloze F je kontrolní seznam návrhových opatření za účelem zamezení systematickým poruchám. Obsahuje:

- Přehled produktu

- Informace o aplikaci

- Bezpečnostní koncept

- Předpovědi životnosti

- FIT

- Výpočty FMEDA – SFF a DC

- Hardwarové bezpečnostní mechanismy

- Popis diagnostiky

- Robustnost EMC

- Provoz v redundantních konfiguracích

- Seznam příloh a dokumentů

Souhrnně lze říci, že certifikace funkční bezpečnosti pro nově zavedenou součást prostřednictvím procesu Route 1S je dlouhá, složitá, časově náročná, intenzivní a ucelená. Naštěstí proces Route 2S, jak je uvedeno výše, je alternativní přístup, který je pro některé součásti realizovatelný.

Route 2S: alternativní proces

Proces známý jako Route 2S je použitelný pro vydaný díl se zkušenostmi a daty z provozu a je označen jako „osvědčený při používání“. Je založen na analýze vrácení od zákazníků a počtu odeslaných zařízení. Nelze ho použít s novými díly, které mají při skutečném použití malý nebo žádný „záznam výkonu“.

Proces Route 2S umožňuje certifikaci SIL, jako by díl byl plně analyzován podle standardu IEC 61508. Je k dispozici návrhářům modulů a systémů, pokud v minulosti úspěšně používali integrovaný obvod objektu a znají četnost poruch z provozu. Díky vestavěným funkcím testování a ověřování spolu s daty o výkonu jsou AD7214-4 a AD7214-8 dobrými kandidáty pro proces Route 2S.

Zahájení procesu Route 2S vyžaduje podrobná a statisticky významná data o vrácení a poruchách v provozu. Tento požadavek je pro dodavatele integrovaných obvodů mnohem obtížnější splnit než pro dodavatele desek nebo modulů. Důvodem je, že prvně jmenovaní obecně nemají dostatečné znalosti o konečné aplikaci nebo o tom, jaké procento jednotek s poruchami v provozu se jim vrací k analýze.

Závěr

Proces Route 1S pro funkčně bezpečnou certifikaci nových produktů je důkladný, ucelený a podrobný. Je také technicky náročný a rozhodně časově náročný. Oproti tomu proces Route 2S umožňuje, aby byly vydané produkty certifikovány na základě zkušeností a poruch z provozu a dat analýzy. Toto je užitečný způsob, který je podporován integrovanými obvody rozhraní AD7214-4 a AD7214-8 RTD, protože mají požadovanou historii. Stejně důležité je, že tyto integrované obvody obsahují mnoho diagnostických a samotestovacích funkcí a prvků, které z nich činí vhodné kandidáty pro takovou certifikaci.

Související obsah

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.