Využijte rychlou cestu FPGA k vytváření vysoce výkonných a energeticky účinných aplikací AI na okraji

Contributed By DigiKey's North American Editors

2021-01-12

Konstruktéři, kteří chtějí implementovat algoritmy umělé inteligence (AI) na inferenční procesory na okraji, jsou pod neustálým tlakem na snížení spotřeby energie a doby vývoje, i když se zvyšují nároky na zpracování. Zvlášť efektivní kombinaci rychlosti a energetické účinnosti pro implementaci inferenčních procesorů neuronové sítě (NN) požadovaných pro AI na okraji nabízejí hradlová pole programovatelná v provozu (FPGA). Pro vývojáře, kteří FPGA neznají, se však konvenční metody vývoje FPGA mohou zdát složité, což často vede vývojáře k méně optimálním řešením.

Tento článek popisuje jednodušší koncepci společnosti Microchip Technology, která umožňuje vývojářům obejít tradiční vývoj FPGA a vytvářet trénované NN pomocí FPGA a sady pro vývoj softwaru (SDK) nebo použít sadu videa na bázi FPGA k okamžitému přechodu do vývoje aplikací pro inteligentní integrované vidění.

Proč používat AI na okraji?

Edge computing přináší řadu výhod pro aplikace internetu věcí (IoT) v různých segmentech, jako je průmyslová automatizace, bezpečnostní systémy, inteligentní domácnosti a další. V aplikaci Industrial IoT (IIoT) zaměřené na továrnu může edge computing dramaticky zlepšit dobu odezvy ve smyčkách řízení procesu tím, že eliminuje zpoždění zpáteční cesty cloudovým aplikacím. Podobně může okrajový bezpečnostní systém nebo zámek inteligentních domů fungovat i nadále, i když dojde k náhodnému nebo úmyslnému ztrátě připojení k cloudu. V mnoha případech může použití edge computingu v jakékoli z těchto aplikací pomoci snížit celkové provozní náklady snížením závislosti produktu na cloudových prostředcích. Spíše než čelit neočekávané potřebě dalších drahých cloudových zdrojů, jak roste poptávka po jejich produktech, mohou se vývojáři spolehnout na místní možnosti zpracování zabudované do jejich produktů, které jim pomohou udržet stabilnější provozní náklady.

Rychlé přijetí a zvýšená poptávka po inferenčních modelech strojového učení (ML) dramaticky zesiluje význam edge computingu. Pro vývojáře pomáhá místní zpracování inferenčních modelů snížit latenci odezvy a náklady na cloudové zdroje potřebné pro cloudovou inferenci. Používání místních inferenčních modelů dodává uživatelům jistotu, že jejich produkty budou i nadále fungovat navzdory občasné ztrátě připojení k internetu nebo změnám v cloudových nabídkách dodavatele produktů. Kromě toho obavy o zabezpečení a soukromí mohou dále zvyšovat potřebu lokálního zpracování a inference, aby se omezilo množství citlivých informací přenášených do cloudu přes veřejný internet.

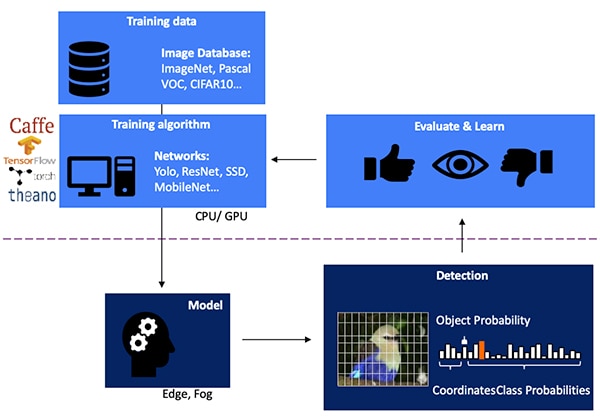

Vývoj inferenčního modelu NN pro detekci objektů na základě vidění je tvořen vícestupňovým procesem počínaje tréninkem modelu, který se obvykle provádí na ML rámci, jako je TensorFlow, pomocí veřejně dostupných snímků se štítky nebo snímků s vlastními štítky. Z důvodu požadavků na zpracování se trénink modelu obvykle provádí s grafickými jednotkami (GPU) v cloudu nebo na jiné vysoce výkonné výpočetní platformě. Po dokončení tréninku se model převede na inferenční model, který je schopen běžet na prostředcích fog computingu na okraji nebo v mlze a dodat výsledky inference jako sadu pravděpodobností třídy objektů (obrázek 1).

Obrázek 1: Implementace inferenčního modelu pro AI na okraji leží na konci vícestupňového procesu vyžadujícího školení a optimalizaci NN v rámci s využitím dostupných nebo vlastních dat školení. (Zdroj obrázku: Microchip Technology)

Obrázek 1: Implementace inferenčního modelu pro AI na okraji leží na konci vícestupňového procesu vyžadujícího školení a optimalizaci NN v rámci s využitím dostupných nebo vlastních dat školení. (Zdroj obrázku: Microchip Technology)

Proč jsou inferenční modely výpočetně náročné

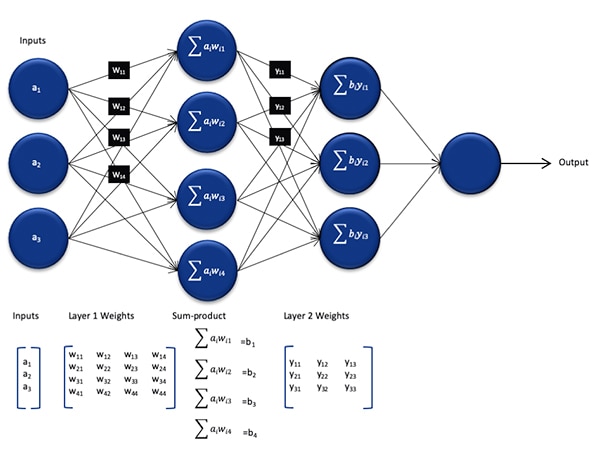

I když je velikost a složitost ve srovnání s modelem použitým během tréninkového procesu snížena, inferenční model NN stále představuje výpočetní problém pro procesory pro všeobecné účely kvůli velkému počtu výpočtů, které vyžaduje. Ve své obecné formě obsahuje hluboký model NN několik vrstev sad neuronů. V každé vrstvě v plně připojené síti je pro každý neuron nij nutné vypočítat součet produktů každého vstupu s přidruženou hmotností wij (obrázek 2).

Obrázek 2: Počet výpočtů požadovaných pro inferenci s NN může způsobit značnou výpočetní zátěž. (Zdroj obrázku: Microchip Technology)

Obrázek 2: Počet výpočtů požadovaných pro inferenci s NN může způsobit značnou výpočetní zátěž. (Zdroj obrázku: Microchip Technology)

Na obrázku 2 není znázorněn další výpočetní požadavek uložený aktivační funkcí, která upravuje výstup každého neuronu mapováním záporných hodnot na nulu, mapováním hodnot větších než 1: 1 a podobnými funkcemi. Výstup aktivační funkce pro každý neuron nij slouží jako vstup do další vrstvy i + 1 a pokračuje tímto způsobem pro každou vrstvu. Nakonec výstupní vrstva modelu NN produkuje výstupní vektor představující pravděpodobnost, že původní vstupní vektor (nebo matice) odpovídá jedné z tříd (nebo štítků) použitých během supervizovaného procesu učení.

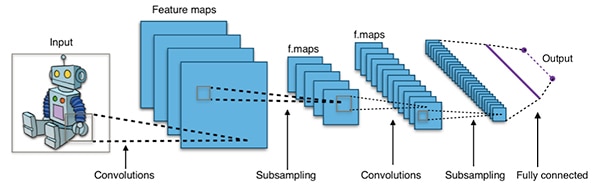

Efektivní modely NN jsou postaveny na architekturách, které jsou mnohem větší a složitější než reprezentativní obecná architektura NN uvedená výše. Například typická konvoluční síť NN (CNN) používaná k detekci obrazových objektů aplikuje tyto principy po částech a snímáním šířky, výšky a barevné hloubky vstupního obrazu vytváří řadu map funkcí, které v konečné fázi přinesou výstupní predikční vektor (obrázek 3).

Obrázek 3: CNN používané k detekci obrazových objektů zahrnují velké množství neuronů v mnoha vrstvách, což klade větší nároky na výpočetní platformu. (Zdroj obrázku: Aphex34 CC BY-SA 4.0)

Obrázek 3: CNN používané k detekci obrazových objektů zahrnují velké množství neuronů v mnoha vrstvách, což klade větší nároky na výpočetní platformu. (Zdroj obrázku: Aphex34 CC BY-SA 4.0)

Využívání FPGA k urychlení matematiky NN

Ačkoli se stále objevuje řada možností spouštění inferenčních modelů na okraji, několik alternativ poskytuje optimální kombinaci flexibility, výkonu a energetické účinnosti potřebné pro praktickou vysokorychlostní inferenci na okraji. Mezi snadno dostupnými alternativami pro AI na okraji jsou FPGA obzvláště účinné, protože mohou poskytovat vysoce výkonné hardwarové provádění operací náročných na výpočet při nízké spotřebě energie.

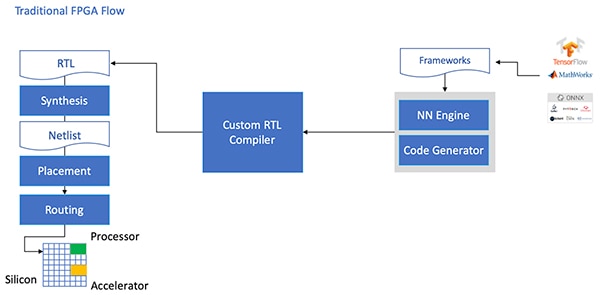

Přes své výhody jsou FPGA někdy obcházeny kvůli tradičnímu vývojovému směru, který může být zklamáním pro vývojáře bez rozsáhlých zkušeností s FPGA. K vytvoření efektivní implementace FPGA modelu NN generovaného rámcem NN by vývojář potřeboval porozumět nuancím převodu modelu do jazyka pro přenos registrů (RTL), syntézy designu a zpracování konečného místa a směrování fyzického designu fázi k vytvoření optimalizované implementace (obrázek 4).

Obrázek 4: Aby vývojáři mohli implementovat model NN na FPGA, potřebovali doposud pochopit, jak převést své modely na RTL a pracovat pomocí tradičního toku FPGA. (Zdroj obrázku: Microchip Technology)

Obrázek 4: Aby vývojáři mohli implementovat model NN na FPGA, potřebovali doposud pochopit, jak převést své modely na RTL a pracovat pomocí tradičního toku FPGA. (Zdroj obrázku: Microchip Technology)

Pomocí specializovaného softwaru a souvisejícího duševního vlastnictví (IP) PolarFire FPGA poskytuje společnost Microchip Technology řešení, díky kterému se vysoce výkonné inference na okraji s nízkou spotřebou stávají široce dostupnými pro vývojáře bez zkušeností s FPGA.

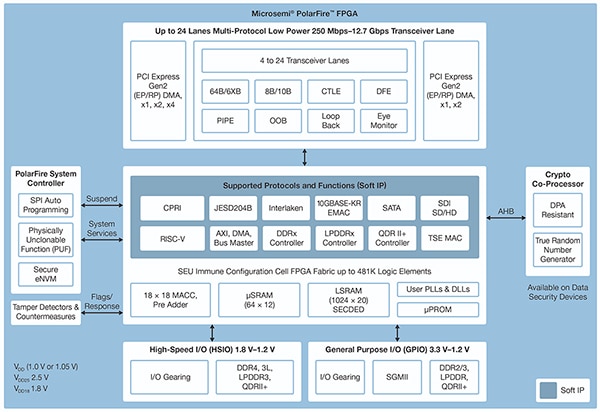

PolarFire FPGA jsou vyrobeny z pokročilé energeticky nezávislé technologie procesu a jsou navrženy tak, aby maximalizovaly flexibilitu a výkon při minimalizaci spotřeby energie. Spolu s rozsáhlou řadou vysokorychlostních rozhraní pro komunikaci a vstup/výstup (I/O) obsahují hlubokou strukturu FPGA, která je schopna podporovat pokročilé funkce pomocí měkkých IP jader, včetně procesorů RISC-V, pokročilých řadičů pamětí a dalších standardní subsystémů rozhraní (obrázek 5).

Obrázek 5: Architektura Microchip Technology PolarFire poskytuje hlubokou strukturu navrženou tak, aby podporovala vysoce výkonné konstrukční požadavky, včetně implementace výpočetně náročného inferenčního modelu. (Zdroj obrázku: Microchip Technology)

Obrázek 5: Architektura Microchip Technology PolarFire poskytuje hlubokou strukturu navrženou tak, aby podporovala vysoce výkonné konstrukční požadavky, včetně implementace výpočetně náročného inferenčního modelu. (Zdroj obrázku: Microchip Technology)

Konstrukce PolarFire FPGA poskytuje rozsáhlou sadu logických prvků a specializovaných bloků, podporovaných v různých kapacitách různými členy skupiny PolarFire FPGA, včetněMPF100T ,MPF200T ,MPF300T , aMPF500T série (tabulka 1).

|

Tabulka 1: V řadě PolarFire jsou k dispozici různé vlastnosti a kapacity konstrukcí FPGA. (Zdroj tabulky: DigiKey, převzato z datového listu společnosti Microchip Technology PolarFire)

Mezi funkce zvláštního zájmu pro zrychlení inference zahrnuje architektura PolarFire vyhrazený matematický blok, který poskytuje 18bitovou × 18bitovou podepsanou funkci multiply-accumulate (MAC) s předčítačem. Režim integrovaného produktu s tečkami používá jeden matematický blok k provedení dvou 8bitových operací násobení, což poskytuje mechanismus ke zvýšení kapacity využitím výhod zanedbatelného dopadu kvantizace modelu na přesnost.

Kromě zrychlení matematických operací architektura PolarFire pomáhá zmírnit přetížení paměti, ke kterému dochází při implementaci inferenčních modelů na architekturách pro obecné účely, jako jsou malé distribuované paměti pro ukládání průběžných výsledků vytvořených během provádění algoritmu NN. Váhy a hodnoty zkreslení modelu NN lze také uložit do 16bitové a 18bitové paměti pro čtení (ROM) určené pro čtení (ROM) vytvořené z logických prvků umístěných v blízkosti matematického bloku.

V kombinaci s dalšími funkcemi konstrukce PolarFire FPGA jsou matematické bloky základem pro vyšší úroveň CoreVectorBlox IP společnosti Microchip Technology. Ta slouží jako flexibilní NN procesor schopný spouštět různé typy NN. Spolu se sadou řídicích registrů obsahuje CoreVectorBlox IP tři hlavní funkční bloky:

- Mikrokontrolér: Jednoduchý měkký procesor RISC-V, který čte velký binární objekt firmwaru Microchip (BLOB) a uživatelský specifický soubor NN BLOB z externího úložiště. Řídí celkové operace CoreVectorBlox prováděním pokynů z firmwaru BLOB.

- Maticový procesor (MXP): Měkký procesor obsahující osm 32bitových aritmetických logických jednotek (ALU) a určený k provádění paralelních operací s datovými vektory pomocí elementárních tenzorových operací, včetně add, sub, xor, shift, mul, dotprod a dalších, podle potřeby pomocí smíšené 8bitové, 16bitové a 32bitové přesnosti.

- CNN accelerator: Zrychluje operace MXP pomocí dvourozměrného pole funkcí MAC implementovaných pomocí matematických bloků a pracujících s 8bitovou přesností.

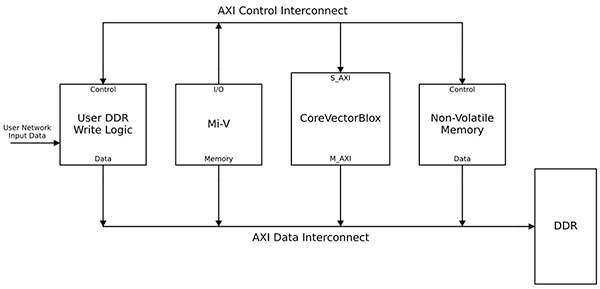

Kompletní systém zpracování NN by kombinoval IP blok CoreVectorBlox, paměť, řadič paměti a hostitelský procesor, jako je jádro softwarového procesoru Microsoft RISC-V (Mi-V) (obrázek 6).

Obrázek 6: Blok CoreVectorBlox IP spolupracuje s hostitelským procesorem, jako je mikrokontrolér Mi-V RISC-V od společnosti Microchip, na implementaci inferenčního modelu NN. (Zdroj obrázku: Microchip Technology)

Obrázek 6: Blok CoreVectorBlox IP spolupracuje s hostitelským procesorem, jako je mikrokontrolér Mi-V RISC-V od společnosti Microchip, na implementaci inferenčního modelu NN. (Zdroj obrázku: Microchip Technology)

V implementaci videosystému by hostitelský procesor načetl firmware a síťové BLOBy ze systémové paměti flash a zkopíroval je do paměti s náhodným přístupem (RAM) s dvojitou rychlostí dat (RAM) pro použití v bloku CoreVectorBlox. Jakmile dorazí videosnímky, hostitelský procesor je zapíše do paměti DDR RAM a signalizuje bloku CoreVectorBlox, aby zahájil zpracování obrazu. Po spuštění inferenčního modelu definovaného v síťovém BLOBu zapíše blok CoreVectorBlox výsledky včetně klasifikace obrázků zpět do paměti DDR RAM pro použití cílovou aplikací.

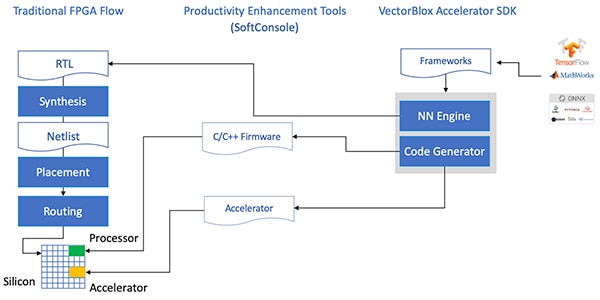

Vývojový tok zjednodušuje implementaci NN FPGA

Microchip chrání vývojáře před složitostí implementace inferenčního modelu NN na FPGA PolarFire. Místo toho, aby se zabývali podrobnostmi tradičního toku FPGA, vývojáři modelů NN pracují se svými NN rámci jako obvykle a načítají výsledný model do Microchip TechnologySada pro vývoj softwaru VectorBlox Accelerator (SDK). Sada SDK generuje požadovanou sadu souborů, včetně těch, které jsou potřebné pro normální vývojový proces FPGA, a výše zmíněné soubory firmwaru a sítě BLOB (obrázek 7).

Obrázek 7: Sada VectorBlox Accelerator SDK spravuje podrobnosti implementace modelu NN na FPGA a automaticky generuje soubory potřebné k návrhu a spuštění inferenčního modelu založeného na FPGA. (Zdroj obrázku: Microchip Technology)

Obrázek 7: Sada VectorBlox Accelerator SDK spravuje podrobnosti implementace modelu NN na FPGA a automaticky generuje soubory potřebné k návrhu a spuštění inferenčního modelu založeného na FPGA. (Zdroj obrázku: Microchip Technology)

Protože tok SDK VectorBlox Accelerator překrývá design NN na procesoru NN implementovaném v FPGA, mohou různé NN běžet na stejném designu FPGA bez nutnosti opakovat tok syntézy návrhu FPGA. Vývojáři vytvářejí pro výsledný systém kód C / C ++ a jsou schopni přepínat modely v rámci systému za běhu nebo spouštět modely současně pomocí časového segmentu.

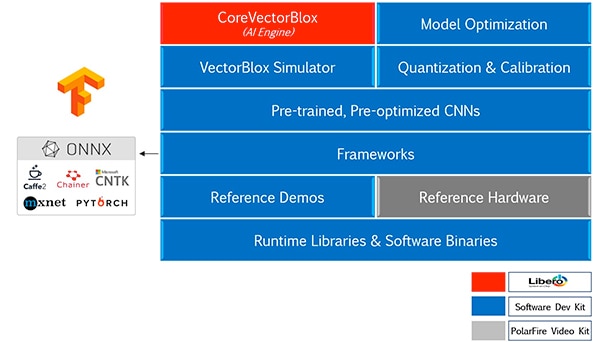

Sada VectorBlox Accelerator SDK spojuje technologii Microchip Libero Konstrukční platforma FPGA s komplexní sadou funkcí pro vývoj inferenčních modelů NN. Spolu s optimalizací, kvantizací a kalibrací služeb poskytuje SDK simulátor NN, který umožňuje vývojářům používat stejné soubory BLOB k vyhodnocení jejich modelu před jejich použitím při implementaci hardwaru FPGA (obrázek 8).

Obrázek 8: Sada VectorBlox Accelerator SDK poskytuje komplexní sadu služeb určených k optimalizaci implementace inferenčních modelů FPGA generovaných rámcem. (Zdroj obrázku: Microchip Technology)

Obrázek 8: Sada VectorBlox Accelerator SDK poskytuje komplexní sadu služeb určených k optimalizaci implementace inferenčních modelů FPGA generovaných rámcem. (Zdroj obrázku: Microchip Technology)

Sada VectorBlox Accelerator SDK podporuje modely ve formátu Open Neural Network Exchange (ONNX) i modely z celé řady rámců včetně TensorFlow, Caffe, Chainer, PyTorch a MXNET. Podporované architektury CNN zahrnují MNIST, verze MobileNet, ResNet-50, Tiny Yolo V2 a Tiny Yolo V3. Společnost Microchip pracuje na rozšíření podpory tak, aby zahrnovala většinu sítí v otevřené modelové zoo sady open-source nástrojů OpenVINO s předem vyškolenými modely včetně Yolo V3, Yolo V4, RetinaNet a SSD-MobileNet.

Video kit ukazuje FPGA inferenci

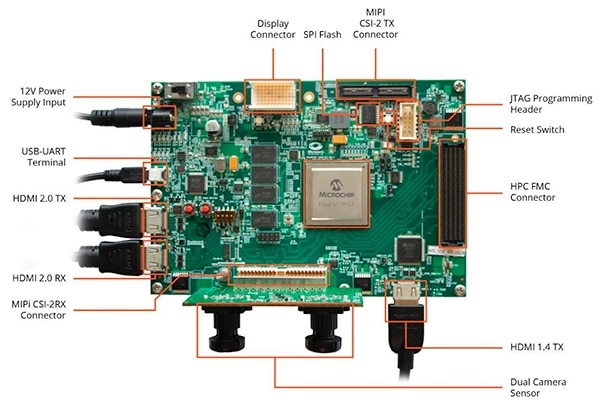

Abychom vývojářům pomohli rychle přejít k vývoji aplikací pro inteligentní vestavěné vidění, poskytuje společnost Microchip Technology komplexní ukázkovou aplikaci navrženou pro provoz na platformě PolarFire FPGA Video and Imaging Kit MPF300-VIDEO-KIT a referenčním designu od této společnosti.

Deska sady založená na platformě Microchip MPF300T PolarFire FPGA kombinuje snímač duálního fotoaparátu, paměť RAM s dvojnásobnou rychlostí přenosu dat 4 (DDR4), flash paměť, správu napájení a řadu rozhraní (obrázek 9).

Obrázek 9: Sada MPF300-VIDEO-KIT PolarFire FPGA Video and Imaging Kit a související software poskytuje vývojářům rychlý začátek inference založené na FPGA v aplikacích smart embedded vision. (Zdroj obrázku: Microchip Technology)

Obrázek 9: Sada MPF300-VIDEO-KIT PolarFire FPGA Video and Imaging Kit a související software poskytuje vývojářům rychlý začátek inference založené na FPGA v aplikacích smart embedded vision. (Zdroj obrázku: Microchip Technology)

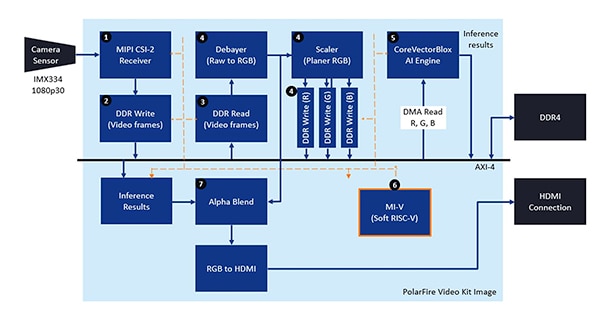

Sada je dodávána s kompletním projektem Libero, který se používá ke generování firmwaru a síťových souborů BLOB. Po naprogramování souborů BLOB do vestavěné flash paměti vývojáři kliknutím na spouštěcí tlačítko Libero spustí demonstraci, která zpracovává video snímky ze snímače kamery a zobrazuje výsledky inference na displeji (obrázek 10).

Obrázek 10: Sada Microchip Technology PolarFire FPGA Video and Imaging Kit ukazuje, jak navrhnout a použít implementaci FPGA inteligentního vestavěného kamerového systému založeného na procesoru Microchip CoreVectorBlox NN. (Zdroj obrázku: Microchip Technology)

Obrázek 10: Sada Microchip Technology PolarFire FPGA Video and Imaging Kit ukazuje, jak navrhnout a použít implementaci FPGA inteligentního vestavěného kamerového systému založeného na procesoru Microchip CoreVectorBlox NN. (Zdroj obrázku: Microchip Technology)

Pro každý vstupní video snímek provede systém založený na FPGA následující kroky (s čísly kroků, které odpovídají obrázku 10):

- Vložte rámeček z fotoaparátu

- Rámeček uložte do paměti RAM

- Přečtěte si snímek z RAM

- Převeďte surový obraz na RGB, srovnejte RGB a výsledek uložte do paměti RAM

- Softwarový procesor Mi-V RISC-V spouští jádro CoreVectorBlox, které načítá obraz z paměti RAM, provádí inferenci a ukládá výsledky pravděpodobnosti klasifikace zpět do paměti RAM

- Mi-V používá výsledky k vytvoření překryvného rámečku s ohraničujícími rámečky, výsledkům klasifikace a dalším metadatům a uloží rámeček do paměti RAM

- Původní rámec je zkombinován s rámcem překrytí a zapsán do HDMI zobrazení

Demonstrace podporuje akceleraci modelů Tiny Yolo V3 a MobileNet V2, ale vývojáři mohou spustit další modely podporované sadou SDK pomocí výše popsaných metod provedením malé změny kódu a přidání názvu modelu a metadat do existujícího seznamu obsahujícího dva výchozí modely.

Závěr

Algoritmy AI, jako jsou modely NN, obvykle ukládají výpočetně náročné úlohy, které vyžadují robustnější výpočetní prostředky, než jaké jsou k dispozici u procesorů pro všeobecné účely. Zatímco FPGA jsou dobře vybaveny, aby splňovaly požadavky na výkon a nízkou spotřebu při spouštění inferenčního modelu, konvenční metody vývoje FPGA se mohou zdát složité, což často vede vývojáře k neoptimálním řešením.

Jak je ukázáno, pomocí specializované IP a softwaru od Microchip Technology mohou vývojáři bez zkušeností s FPGA implementovat inferenční konstrukce, které lépe splňují požadavky na výkonnost, výkon a harmonogram projektu.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.