Agilní RF transceiver lze využívat v adaptivním komunikačním systému SDR pro letectví, kosmonautiku a obranu

Contributed By DigiKey's North American Editors

2023-11-30

Konstruktéři leteckých a obranných systémů (ADEF) čelí neutuchající poptávce po nižších výkonech a kompaktnějších komunikačních systémech schopných pohotově reagovat na prostředí dynamických signálů. Technologie rádia definovaného softwarem (SDR), která překračuje tradiční radiofrekvenční architektury, může pomoci naplnit rychle se měnící požadavky na radiová zařízení s adaptivní zpětnou vazbou a dvojitou obálkou (ADEF). Implementace technologie SDR představuje řadu problémů pro splnění jak funkčních požadavků, tak i potřeby snížení velikosti, hmotnosti a výkonu (SWaP).

Tento článek popisuje efektivnější řešení technologie SDR od společnosti Analog Devices, která mohou zjednodušit návrhy nízkoenergetických, kompaktních a agilních komunikačních systémů bez snížení výkonu.

Vznikající výzvy vyvolávají náročnější požadavky

Konstruktéři čelí poptávce po efektivnější komunikaci v rostoucím počtu průmyslových a kriticky důležitých aplikací, včetně zabezpečené rádiové komunikace, adaptivního radaru, elektronického boje a vylepšené GPS navigace. Tyto nové výzvy vyvolávají potřebu vylepšeného širokopásmového provozu, vyššího dynamického rozsahu, větší frekvenční agilnosti a rekonfigurovatelnosti. Tyto náročnější funkční požadavky však mohou být v rozporu s potřebou nižší hodnoty SWaP, protože komunikační systémy přecházejí na menší bateriově napájené platformy, včetně bezpilotních letounů (UAS) a přenosných jednotek.

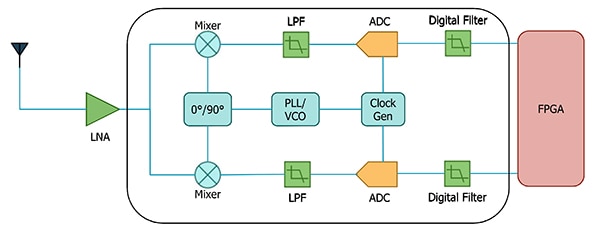

Konstrukční řešení založená na tradičních diskrétních superheterodynních rádiových architekturách nabízejí vysoký výkon, široký dynamický rozsah a minimální rušivý šum. Pro konstruktéry znamená problém izolace požadovaného signálu od mezifrekvence (IF) v jádru této koncepce obvykle složité návrhy s vysokou hodnotou SWaP a malou nebo nulovou možností rekonfigurace (obrázek 1).

Obrázek 1: ačkoli tradiční superheterodynní radiové architektury mohou splnit požadované výkonnostní charakteristiky, jejich složitost jim brání splnit nové cílové požadavky na minimální hodnotu SWaP. (Zdroj obrázku: Analog Devices)

Obrázek 1: ačkoli tradiční superheterodynní radiové architektury mohou splnit požadované výkonnostní charakteristiky, jejich složitost jim brání splnit nové cílové požadavky na minimální hodnotu SWaP. (Zdroj obrázku: Analog Devices)

Naproti tomu architektury s přímou konverzí (zero-IF) snižují jak požadavky na filtraci, tak i potřebu analogově-digitálních převodníků (ADC) s velmi vysokou šířkou pásma, což vede k jednoduššímu návrhu s možností implementace na jediném čipu (obrázek 2).

Obrázek 2: ačkoli mohou radiová zařízení s nulovou mezifrekvencí (IF) naplnit potřebu vyššího výkonu a nižší hodnoty SWaP, izolace signálu je náročná. (Zdroj obrázku: Analog Devices)

Obrázek 2: ačkoli mohou radiová zařízení s nulovou mezifrekvencí (IF) naplnit potřebu vyššího výkonu a nižší hodnoty SWaP, izolace signálu je náročná. (Zdroj obrázku: Analog Devices)

Navzdory zjevným výhodám má však architektura přímé konverze své vlastní implementační problémy omezující její široké přijetí. V této architektuře je signál převeden na vysokofrekvenční (RF) nosnou vlnu na frekvenci lokálního oscilátoru (LO), avšak chyby offsetu stejnosměrného proudu (DC) a svod oscilátoru LO mohou vést k šíření chyb signálovým řetězcem. Kromě toho mohou rozdíly v signálových cestách, dokonce i v rámci stejného čipu, zavádět zesílení nebo fázový nesoulad soufázového (I) a kvadraturního (Q) signálu, což má za následek kvadraturní chybu, která může ohrozit izolaci signálu.

Ačkoli technologie SDR nabízí potenciál k překonání omezení tradičních rádiových architektur, jen málo řešení dokáže řešit širší požadavky spojené s aplikacemi ADEF. Použitím RF transceiveru ADRV9002 od společnosti Analog Devices mohou vývojáři snadno naplnit potřebu vyššího výkonu a funkčnosti s nižší hodnotou SWaP, kterou takové aplikace vyžadují.

Integrovaná funkčnost poskytuje optimalizovaný výkon s omezenou hodnotou SWaP

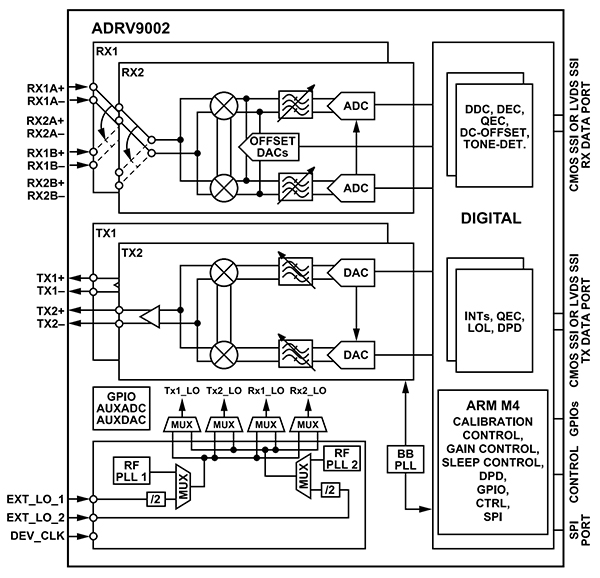

Obvod ADRV9002 podporující frekvenční rozsah 30 MHz až 6 000 MHz je vysoce integrovaný transceiver, který obsahuje všechny funkce RF, smíšeného signálu a digitální funkce požadované pro podporu široké škály aplikačních požadavků. Tento obvod, který umožňuje duplexní provoz s časovým (TDD) i frekvenčním (FDD) dělením, nabízí samostatné dvoukanálové přijímací a vysílací subsystémy s přímou konverzí zahrnující programovatelné digitální filtry, korekci DC offsetu a korekci kvadraturních chyb (QEC).

V rámci syntezátorového subsystému na čipu má obvod ADRV9002 dvě samostatné cesty fázového závěsu (PLL): jednu pro vysokofrekvenční RF cestu a druhou pro digitální hodiny a taktovací signály převodníku. A nakonec blok digitálního zpracování signálu obvodu obsahuje vestavěný procesor Arm® M4, který obsluhuje samokalibraci a řídicí funkce (obrázek 3).

Obrázek 3: RF transceiver ADRV9002 integruje duální příjmové (RX) a vysílací (TX) subsystémy. (Zdroj obrázku: Analog Devices)

Obrázek 3: RF transceiver ADRV9002 integruje duální příjmové (RX) a vysílací (TX) subsystémy. (Zdroj obrázku: Analog Devices)

Obvod ADRV9002, který dokáže pracovat v režimu nulové nebo nízké mezifrekvence (IF) pro aplikace citlivé na fázový šum, obsahuje subsystémy vysílače a přijímače nabízející kompletní signálové řetězce. Každý vysílací subsystém poskytuje dvojici digitálně-analogových převodníků (DAC), filtrů a směšovačů, které rekombinují signály I a Q a modulují je na nosnou přenosovou frekvenci.

Každý subsystém přijímače integruje odporovou vstupní síť na regulaci zisku, která napájí pasivní směšovač v proudovém režimu. Transimpedanční zesilovač následně převádí proudový výstup směšovače na napěťovou úroveň, která je digitalizována A/D převodníkem s vysokým dynamickým rozsahem. Během dostupných slotů vysílače při provozu v režimu TDD nebo v aplikacích FDD, kde se používá pouze jeden přijímací systém, lze nevyužité vstupy přijímače používat k monitorování kanálů vysílače na svod oscilátoru LO a QEC, nebo lze tyto vstupy používat k monitorování úrovní výstupního signálu výkonového zesilovače (PA).

Druhá zmíněná schopnost vstupuje do hry jako součást funkce integrovaného digitálního předzkreslení (DPD) transceiveru ADRV9002, která na základě monitorování úrovně signálu jeho výkonového zesilovače aplikuje vhodné předzkreslení potřebného k linearizaci výstupu. Tato schopnost umožňuje obvodu ADRV9002 vybudit výkonový zesilovač blíže k saturaci a optimalizovat tak jeho účinnost.

Vyladění výkonu a spotřeby energie

Obvod ADRV9002 představuje plně integrované řešení v kulovém mřížkovém poli (BGA) s pouzdrem typu CSP (chip scale package) se 196 kuličkami, které rovněž minimalizuje velikost a hmotnost pro komunikační systémy SDR ADEF. Aby obvod ADRV9002 pomohl vývojářům dále optimalizovat spotřebu energie, integruje několik funkcí navržených speciálně jako pomoc k nalezení vhodné rovnováhy mezi výkonem a spotřebou.

Vývojáři mohou na úrovni bloků používat škálování výkonu v jednotlivých blocích signálových cest a vyměnit tak snížený výkon za nižší spotřebu energie. Kromě toho lze bloky v příjmových (RX) a vysílacích rámcích (TX) režimu TDD deaktivovat a obětovat tak časy vybavení RX/TX nebo TX/RX ve prospěch nižší spotřeby energie. Jako další podporu schopnosti vývojářů optimalizovat poměr výkonu a spotřeby energie obsahuje každý subsystém přijímače ADRV9002 dva páry A/D převodníků. Jeden pár obsahuje vysoce výkonné sigma-delta A/D převodníky, zatímco druhý pár jej může v případě kritické spotřeby energie nahradit.

Pro aplikace charakterizované periodickými úseky nečinnosti lze použít monitorovací režim RX obvodu ADRV9002. V tomto režimu se obvod ADRV9002 střídavě přepíná mezi režimem spánku s minimální spotřebou a stavem detekce v naprogramovaném pracovním cyklu. Ve stavu detekce obvod aktivuje přijímač a pokusí se získat signál v šířce pásma a frekvenci RX LO naprogramované vývojářem. Pokud obvod ADRV9002 naměří úroveň výkonu signálu nad naprogramovanou prahovou hodnotou, ukončí režim monitorování a zapne bloky, aby mohl požadovaný signál zpracovávat.

Rychlé prototypování a vývoj

S cílem pomoci konstruktérům k rychlému přechodu na vyhodnocování, prototypování a vývoj poskytuje společnost Analog Devices rozsáhlou hardwarovou a softwarovou podporu systémů založených na obvodu ADRV9002.

Pro podporu hardwaru nabízí společnost Analog Devices následující dvojici karet na bázi obvodu ADRV9002:

- Kartu ADRV9002NP/W1/PCBZ pro nízkopásmové aplikace pracující v rozsahu 30 MHz až 3 GHz.

- Kartu ADRV9002NP/W2/PCBZ pro vysokopásmové aplikace v rozsahu 3 až 6 GHz.

Tyto karty vybavené konektory FMC podporují integrovaný obvod ADRV9002 s regulací napájení a hardwarovými rozhraními, jakož i distribuci taktovacího signálu a vícečipové synchronizace (MCS). Karty se připojují přes FMC konektor k základní desce FPGA, jakou je například vyhodnocovací deska ZCU102 od společnosti AMD na řízení výkonu a aplikací.

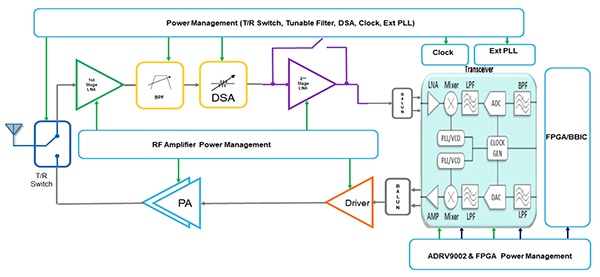

Společnost Analog Devices ve svém balíčku podpory poskytuje pro své rádiové karty ADRV9002NP kompletní schéma a kusovník (BOM). Schéma a kusovník poskytují efektivní výchozí bod pro vývoj vlastního hardwaru pro většinu aplikací. Některé aplikace vyžadují ke splnění konkrétních požadavků na úpravu signálu další RF rozhraní. U takových aplikací potřebují vývojáři k dokončení návrhu pouze několik dalších součástí (obrázek 4).

Obrázek 4: vysoce integrovaný transceiver ADRV9002 umožňuje vývojářům rychlou implementaci specializovaných návrhů. (Zdroj obrázku: Analog Devices)

Obrázek 4: vysoce integrovaný transceiver ADRV9002 umožňuje vývojářům rychlou implementaci specializovaných návrhů. (Zdroj obrázku: Analog Devices)

V tomto příkladu mohou vývojáři pomocí následujících součástí na řízení spotřeby energie od společnosti Analog Devices rychle implementovat vhodné RF rozhraní:

- RF spínač ADRF5160

- Nízkošumový zesilovač (LNA) HMC8411

- Digitálně laditelný pásmový filtr ADMV8526

- Digitální krokový útlumový RF článek (DSA) HMC1119

- Budicí zesilovač HMC8413

- Výkonový zesilovač (PA) HMC8205B

Společnost Analog Devices poskytuje komplexní podporu vývoje softwaru prostřednictvím dokumentace a softwarových balíčků ke stažení. Vývojáři používající výše zmíněný vývojový hardware mohou přistoupit k prototypování a vývoji s použitím řadového softwaru nebo open-source softwarových balíčků od společnosti Analog Devices.

V tomto článku je následující diskuse omezena na řadový software. Další informace o metodologii vývoje pomocí open-source softwaru naleznete v Uživatelské příručce prototypovací platformy ADRV9001/2 od společnosti Analog Devices.Společnost Analog Devices stanoví, že termínem „ADRV9001“ v průvodní dokumentaci se rozumí název skupiny zahrnující obvod ADRV9002 a další členy skupiny produktů ADRV9001. V důsledku toho se odkazy na obvod ADRV9001 v níže uvedeném textu nebo na obrázcích níže vztahují na produkt ADRV9002, který je předmětem tohoto článku.

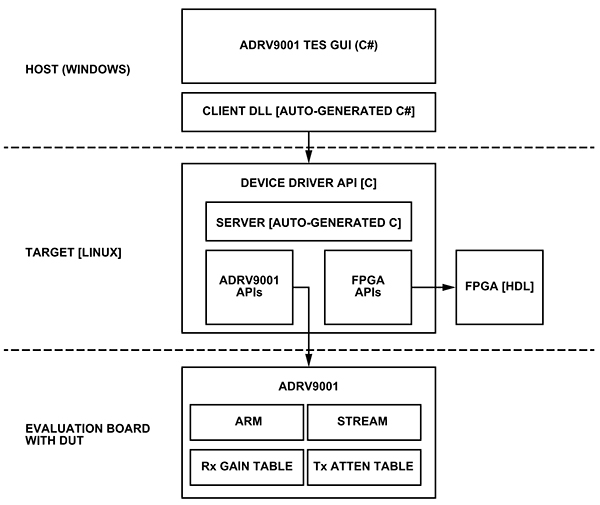

Softwarový nástroj na vyhodnocování transceiveru (TES) na platformě Windows, který je dostupný v rámci distribuce softwarové vývojové sady (SDK) společnosti Analog Devices, poskytuje přístupný výchozí bod pro rychlou konfiguraci a vyhodnocování výkonu transceiveru.

Při vyhodnocování a prototypování pomocí karet na bázi obvodu ADRV9002 od společnosti Analog Devices a vyhodnocovací desky ZCU102 od společnosti AMD poskytuje nástroj TES grafické uživatelské rozhraní (GUI) na konfiguraci hardwaru a sledování zachycených dat (obrázek 5).

Obrázek 5: nástroj TES v balíčku sady SDK umožňuje vývojářům rychlé zahájení vyhodnocování transceiveru ADRV9002 na podporované vyhodnocovací platformě. (Zdroj obrázku: Analog Devices)

Obrázek 5: nástroj TES v balíčku sady SDK umožňuje vývojářům rychlé zahájení vyhodnocování transceiveru ADRV9002 na podporované vyhodnocovací platformě. (Zdroj obrázku: Analog Devices)

Nástroj TES následně automaticky generuje kód v jazyce C#, který lze zkompilovat do prostředí Linux, MATLAB nebo do jazyka Python. Nástroje SDK poskytují kompletní sadu softwarových knihoven a aplikačních programovacích rozhraní (API) včetně balíčku ADRV9001 API vyvinutého pro platformu AMD ZCU102.

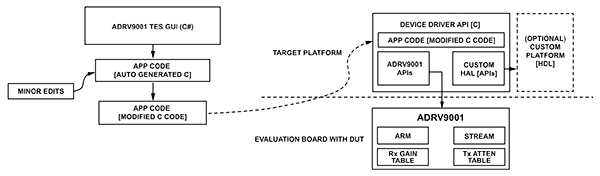

Uspořádání sady SDK také přímo podporuje migraci z vyhodnocování a prototypování pomocí vyhodnocovací desky do vlastního cílového prostředí vývojáře (obrázek 6).

Obrázek 6: architektura sady SDK umožňuje vývojářům snadno rozšířit výsledky jejich hodnocení na vlastní cílovou platformu. (Zdroj obrázku: Analog Devices)

Obrázek 6: architektura sady SDK umožňuje vývojářům snadno rozšířit výsledky jejich hodnocení na vlastní cílovou platformu. (Zdroj obrázku: Analog Devices)

V tomto toku migrace vývojář ponechá software TES automaticky generovat kód jako obvykle. Namísto přímého použití však vývojář nasadí na cílovou platformu upravenou verzi generovaného kódu. V praxi se požadované úpravy omezují hlavně na odstranění volání funkcí odkazujících na hardwarové komponenty rozpoznané nástrojem TES, které jsou však v cílovém systému nepotřebné. Architektura sady SDK zahrnuje rozhraní hardwarové abstraktní vrstvy (HAL) mezi knihovnou ADRV9001 a vývojářským hardwarem, čímž vývojáři pro svůj specifický hardware potřebují pouze vlastní kód implementující kód rozhraní HAL. Díky tomu mohou vývojáři rychle přecházet od vyhodnocování pomocí karet od společnosti Analog Devices a desky od společnosti AMD k vývoji pro vlastní cílové prostředí.

Závěr

Aplikace adaptivní zpětné vazby s dvojitou obálkou (ADEF) čelí rostoucím výzvám ve stále složitějším signálovém prostředí. Aby vývojáři mohli podpořit migraci těchto aplikací na bateriově napájené systémy, potřebují společně s vyhověním požadavkům na vyšší výkon v širším spektru frekvencí také snížit hodnotu parametru SWaP. Pomocí vysoce integrovaného transceiveru od společnosti Analog Devices mohou vývojáři implementovat softwarově definovaná rádiová řešení (SDR), která jsou schopna tyto požadavky řešit efektivněji.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.