Rychle vytváření vysokofrekvenčních hodin s nízkou nestabilitou (jitterem) pomocí modulu translační smyčky

Contributed By DigiKey's North American Editors

2021-08-04

Konstruktéři přístrojových a měřicích systémů vyžadují signály s nízkou nestabilitou (jitterem) a se signálem bez rušivých vlivů, aby poskytly odstup signál/šum (SNR) nebo velikosti vektorů chyb (EVM) požadované ke splnění stále náročnějších požadavků zákazníků. Současně také čelí značnému tlaku na zmenšení místa na desce, snížení nákladů na návrh i na snížení složitosti. Poslední faktor je rozhodující pro zkrácení doby vývoje, aby se mohla zkrátit doba do uvedení na trh.

K tomu, aby se konstruktéři vypořádali s mnoha výzvami aplikací, musí převést svá řešení pro měření přístrojů a měření času z tradičně diskrétních návrhů na zakázku na integrovanější řešení. Důležitým krokem k tomu je použití integrované translační smyčky s fázovým závěsem (PLL). To umožňuje frekvenční převod směrem nahoru signálu tradičního napěťově řízeného oscilátoru (VCO), přičemž nestabilita (jitter) a fázový šum pevného externího lokálního oscilátoru (LO) zůstávají v podstatě zachovány.

V tomto článku pojednáváme o roli translačních smyček k dosažení nejnižšího integrovaného fázového šumu v oboru. Jako příklad se v článku uvádí modul SiP (system-in-package) translační smyčky (TL SiP) ADF4401A od společnosti Analog Devices. Ukážeme si, jak se řeší požadavky na výkon prostřednictvím výstupního signálu s širokopásmovou integrovanou funkcí nestability (jitteru) méně než −10 femtosekund (fs) rms a vylepšenou izolací ke zmírnění rušivých komponent a zároveň se splňují potřeby konstruktérů na integraci, náklady, složitost a dobu do uvedení na trh.

Tradiční fázový závěs vs. translační smyčka

Primárním účelem translační smyčky je generovat výstupní signál synchronizovaný se vstupním referenčním signálem s výrazně sníženým fázovým šumem v pásmu v porovnání s tradičními fázovými závěsy.

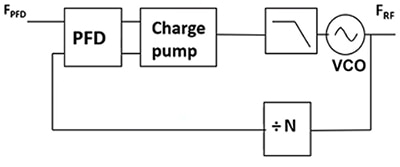

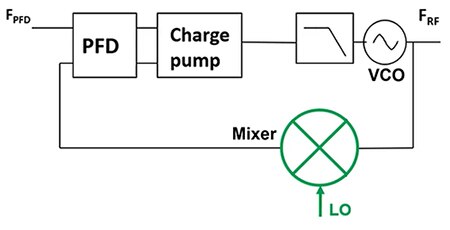

Standardní fázový závěs (PLL) se skládá ze zpětnovazebního systému obsahujícího detektor fázové frekvence (PFD), nábojovou pumpu, dolní propust (LPF), napěťově řízený oscilátor (VCO) a dělič frekvence zpětné vazby N (obrázek 1).

Obrázek 1: Standardní fázový závěs bude synchronizován s nižším referenčním kmitočtem (FPFD) a generuje výstupní frekvenci (FRF). (Zdroj obrázku: Bonnie Baker)

Obrázek 1: Standardní fázový závěs bude synchronizován s nižším referenčním kmitočtem (FPFD) a generuje výstupní frekvenci (FRF). (Zdroj obrázku: Bonnie Baker)

Fázový detektor (PFD) porovnává vstupní referenční fázi s fází zpětnovazebního signálu a generuje sérii impulzů úměrných fázové chybě mezi nimi. Nábojová pumpa přijímá impulsy PFD a převádí je na zdroje proudu nebo zátěžové pulzy, které zase naladí oscilátor VCO na vyšší, nebo nižší frekvenci. Dolní propust odstraňuje vysokofrekvenční energii všech pulzů a převádí je na napětí, které může VCO použít. Výstupní signál VCO je k dokončení smyčky přiváděn zpět do bloku PFD přes děličku N.

Funkce přenosu frekvence na obrázku 1 se vypočítá pomocí rovnice 1:

![]() Rovnice 1

Rovnice 1

Kde FRF je výstupní frekvence.

N je poměr děličky zpětné vazby (může být celočíselný nebo zlomkový).

FPFD je frekvence PFD.

Práh šumu v pásmu na obrázku 1 se vypočítá pomocí rovnice 2:

![]() Rovnice 2

Rovnice 2

Kde FOMPLL je faktor výhodnosti (FOM) fázového šumu v pásmu PLL.

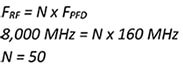

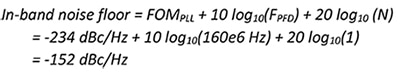

Vezměme si jako příklad FOM s prahem šumu v pásmu −234 dB/Hz, frekvenci PFD (FPFD) 160 MHz a výstupní frekvenci (FRF) 8 GHz.

Pro tento systém se pro výpočet hodnoty N použije rovnice 1:

Rovnice 2 se použije k výpočtu prahu šumu v pásmu:

Ve výše uvedeném výpočtu dělička N výrazně přispívá k celkovému prahu šumu v pásmu s 20log10 (50), což odpovídá 34 dB. Menší hodnota N by snížila práh šumu v pásmu, ale také výstupní frekvenci. Jak tedy vygenerujeme vysokou výstupní frekvenci a udržíme nižší zisk smyčky (N)?

Obrázek 2: U standardního fázového závěsu v tomto příkladu má šum z děličky zpětné vazby (20 log10N)) o 34 dB vyšší pásmový šum ve srovnání se spodní žlutou křivkou, kde N = 1. (Zdroj obrázku: Bonnie Baker)

Obrázek 2: U standardního fázového závěsu v tomto příkladu má šum z děličky zpětné vazby (20 log10N)) o 34 dB vyšší pásmový šum ve srovnání se spodní žlutou křivkou, kde N = 1. (Zdroj obrázku: Bonnie Baker)

Řešením tohoto problému je nahradit N-děličku fází směšování se snižujícím převodem (obrázek 3).

Obrázek 3: Translační smyčka používá ke snížení frekvence oscilátoru VCO na frekvenci PDF namísto tradiční děličky zpětné vazby směšovač. (Zdroj obrázku: Bonnie Baker)

Obrázek 3: Translační smyčka používá ke snížení frekvence oscilátoru VCO na frekvenci PDF namísto tradiční děličky zpětné vazby směšovač. (Zdroj obrázku: Bonnie Baker)

Na obrázku 3 nahrazuje děličku zpětné vazby N směšovač, což má za následek zisk smyčky rovný 1 (N = 1). Tato operace výrazně sníží příspěvek zpětnovazební smyčky k prahu pásmového šumu. Pro výpočet pásmového šumu je nyní hodnota N rovna 1. Pomocí rovnice 2 je práh pásmového šumu pro upravený systém následující:

Nový pásmový šum vykazuje zlepšení o 34 dBc/Hz.

Na obrázku 3 závisí směšovač na extrémně nízkém šumu LO, nazývaném offset LO. FLO ± FRF se musí rovnat FPFD, aby se dosáhlo synchronizace.

U architektury translační smyčky je fázový šum offsetu LO velmi důležitý k dosažení nejlepšího výkonu na RF výstupu. Z tohoto důvodu by technici typicky navrhli offset LO na základě napěťově řízené povrchové akustické vlny (PAV) nebo oscilátorů (VCSO) nebo hřebenových generátorů nebo oscilátorů dielektrických rezonátorů (DRO). POZNÁMKA: Pro podporu při návrhu offsetu LO kontaktujte společnost Analog Devices.

Výzvy spojené s translační smyčkou

Tradičně zahrnuje návrh nízkošumové translační smyčky implementaci mnoha bloků obvodů, což má za následek složitý design, obvykle také velký a s omezenou flexibilitou. Kromě toho musí být celý obvod ověřen a přizpůsoben pro cílovou operaci. Jedním z hlavních konstrukčních problémů je například svod LO (izolace mezi LO a RF) na výstupní signál RF. To je pro konstruktéry velká výzva. U tradičních návrhů přistupují technici obvykle k více iteracím návrhu, aby dosáhli optimalizovaného výkonu a vhodné izolace.

Obrázek 3 ukazuje, jak modul ADF4401A integruje hlavní bloky obvodu, aby poskytl plně přizpůsobené řešení, a eliminuje tradičně obtížné oblasti související s výkonem a izolací v provedeních translačních smyček. Toto programovatelné řešení umožňuje technikům dosáhnout optimalizovaného výkonu na první pokus a zkrátit dobu do uvedení na trh.

Vyhodnocení modulu ADF4401A

Modul ADF4401A je navržen tak, aby pomohl technikům zkrátit dobu do uvedení vysoce výkonných přístrojů na trh pomocí řešení pro generování frekvence s šířkou pásma RF 62,5 MHz až 8 GHz. Při použití směšovače s převodem dolů má modul ADF4401A velmi nízký pásmový šum se širokopásmovou nestabilitou (jitterem) přibližně 9 fs integrovanou od 100 Hz do 100 MHz. Techniky návrhu a uspořádání uvnitř modulu ADF4401A umožňují typický dynamický rozsah bez rušivých vlivů 90 dBc. Velikost pouzdra 18 × 18 × 2,018 mm podstatně zmenšuje prostor na desce ve srovnání s tradičním diskrétním designem.

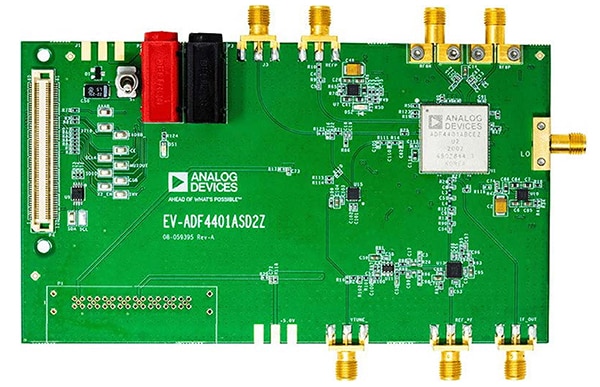

K vyhodnocení výkonu zařízení mohou konstruktéři použít vyhodnocovací desku EV-ADF4401ASD2Z (obrázek 4). Deska obsahuje kompletní translační smyčku, včetně externího PFD (HMC3716), aktivního filtru (LT6200) a multiplexeru (ADG1609).

Obrázek 4: Vyhodnocovací deska EV-ADF4401ASD2Z pro modul translační smyčky ADF4401A obsahuje externí PFD, rozhraní USB a regulátory napětí. (Zdroj obrázku: společnost Analog Devices)

Obrázek 4: Vyhodnocovací deska EV-ADF4401ASD2Z pro modul translační smyčky ADF4401A obsahuje externí PFD, rozhraní USB a regulátory napětí. (Zdroj obrázku: společnost Analog Devices)

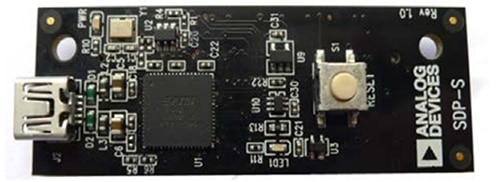

Deska EV-ADF4401ASD2Z obsahuje TL SiP ADF4401A s integrovaným oscilátorem VCO, smyčkovým filtrem (5 MHz), PFD, USB rozhraním a regulátory napětí. Vyhodnocovací deska EV-ADF4401ASD2Z navíc vyžaduje desku řídicí jednotky (sériové) demonstrační platformy systému (SDP) EVAL-SDP-CS1Z (SDP-S) (obrázek 5). Deska poskytuje USB připojení z počítače do vyhodnocovací desky EV-ADF4401ASD2Z, takže ji lze programovat. Deska řídicí jednotky není součástí sady vyhodnocovací desky EV-ADF4401ASD2Z.

Obrázek 5: Deska řídicí jednotky EVAL-SDP-CS1Z (nebo SDP-S) je nutná k zajištění USB připojení z vyhodnocovací desky EV-ADF4401ASD2Z do počítače za účelem programování. (Zdroj obrázku: společnost Analog Devices)

Obrázek 5: Deska řídicí jednotky EVAL-SDP-CS1Z (nebo SDP-S) je nutná k zajištění USB připojení z vyhodnocovací desky EV-ADF4401ASD2Z do počítače za účelem programování. (Zdroj obrázku: společnost Analog Devices)

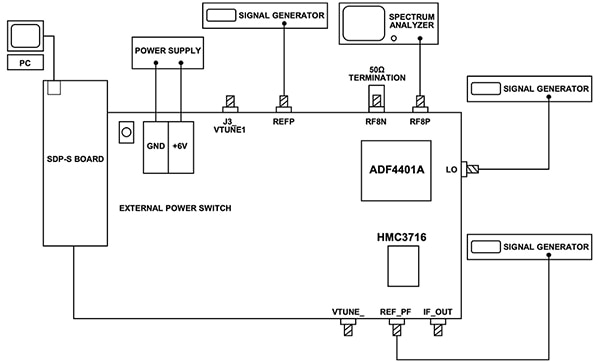

Obrázek 6 mapuje fyzická připojení systému EV-ADF4401ASD2Z. Přidružený software Analysis | Control | Evaluation (ACE) ovládá funkce TL SiP. Napájení je přejímáno z externě použitého 6V napájecího zdroje.

Obrázek 6: Schéma uspořádání EV-ADF4401ASD2Z ukazuje zařízení a připojení potřebná k vyhodnocení modulu ADF4401A, včetně řídicí desky SDP-S, počítače, napájecího zdroje, generátorů signálu a spektrálního analyzátoru. (Zdroj obrázku: společnost Analog Devices)

Obrázek 6: Schéma uspořádání EV-ADF4401ASD2Z ukazuje zařízení a připojení potřebná k vyhodnocení modulu ADF4401A, včetně řídicí desky SDP-S, počítače, napájecího zdroje, generátorů signálu a spektrálního analyzátoru. (Zdroj obrázku: společnost Analog Devices)

Doporučené vybavení pro použití s touto vyhodnocovací deskou zahrnuje počítač se systémem Windows, spektrální analyzátor nebo analyzátor zdroje signálu a tři generátory signálu.

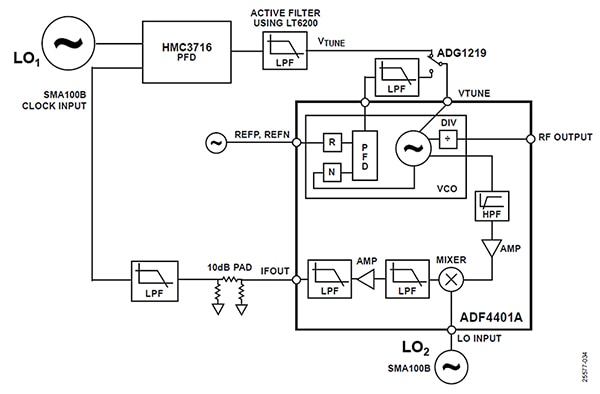

Blokové schéma EV-ADF4401ASD2Z ukazuje modul ADF4401A spolu s PFD HMC3716, operačním zesilovačem LT6200 a přepínačem SPDT ADG1219 společnosti Analog Devices (obrázek 7).

Obrázek 7: Blokové schéma vyhodnocovací desky EV-ADF4401ASD2Z ukazuje klíčové komponenty podporující translační smyčku modulu AD4401A. (Zdroj obrázku: společnost Analog Devices)

Obrázek 7: Blokové schéma vyhodnocovací desky EV-ADF4401ASD2Z ukazuje klíčové komponenty podporující translační smyčku modulu AD4401A. (Zdroj obrázku: společnost Analog Devices)

Je zásadně důležité používat PFD, který může pracovat na vysokých frekvencích, protože to minimalizuje potřebu děliček, které mohou zhoršovat kvalitu odezvy šumu v pásmu. Díky funkci porovnání fází frekvence 1,3 GHz je PFD HMC3716 společnosti Analog Devices ideální pro použití v rozsahu IF ADF4401A. Schopnost takového obvodu porovnávat frekvenci i fázi eliminuje potřebu dalších obvodů pro řízení frekvence na zamýšlenou výstupní frekvenci. HMC3716 se stane externím PFD pro uzavření offsetové smyčky. Vysokofrekvenční provozní rozsah a ultra nízký práh šumu PFD HMC3716 umožňují navrhnout filtry se širokopásmovou smyčkou.

Na obrázku 7 zeslabuje operační zesilovač LT6200 s konfigurací LPF vysokofrekvenční rušení, zatímco přepínač ADG1219 uzavírá translační smyčku systému.

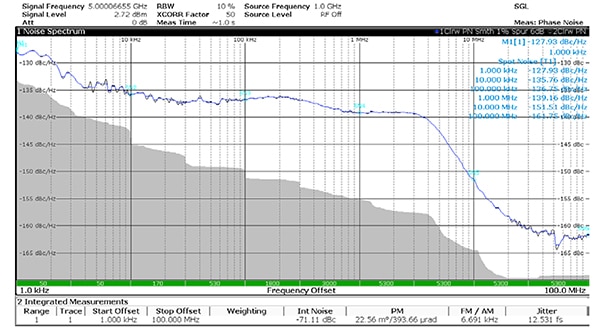

Vyhodnocovací zařízení EV-ADF4401ASD2Z vytváří grafická znázornění pásmového šumu a měření nestability (jitteru), jak je uvedeno na obrázku 8.

Obrázek 8: Fázový šum s jedním postranním pásmem při výstupu 5 GHz, s externí referencí HMC3716 ve výši 500 MHz a externím LO s 4,5 GHz. (Zdroj obrázku: společnost Analog Devices)

Obrázek 8: Fázový šum s jedním postranním pásmem při výstupu 5 GHz, s externí referencí HMC3716 ve výši 500 MHz a externím LO s 4,5 GHz. (Zdroj obrázku: společnost Analog Devices)

Na obrázku 8 je LO2 a vstupem HMC3716 je generátor RF a mikrovlnného signálu SMA100B. Šum v pásmu vyhodnocovací desky LO2 je přibližně −135 dBc/Hz, což je patrné při nízkých offsetech do 300 kHz. LO2, modul ADF4401A, PFD HMC3716 a smyčkový filtr přispívají k pásmovému šumu přibližně −140 dBc/Hz. Interní fázový šum se objevuje mezi 5 MHz a 50 MHz a minimální práh šumu zařízení je přibližně −160 dBc/Hz. Všechny tyto faktory společně tvoří celkovou efektivní nestabilitu (jitter) 12,53 fs.

Závěr

Vysokorychlostní přístrojové systémy vyžadují hodiny s extrémně nízkou nestabilitou (jitterem), aby bylo zajištěno, že výstupní data zůstanou neohrožena. Úkolem techniků je najít vhodná zařízení, která mohou vybudovat vysokorychlostní gigahertzový taktovací systém. Translační smyčka modulu ADF4401A výrazně zjednodušuje výběr zařízení pro budování taktovacího systému a poskytuje kompaktní modul, který zajišťuje nízkou nestabilitu (jitter) na vyšších frekvencích a zároveň snižuje prostor na desce, náklady a zkracuje dobu uvedení na trh.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.