Poznejte různé funkční a bezpečnostní požadavky s vícejádrovými procesory

Contributed By DigiKey's North American Editors

2020-10-01

U automobilů, průmyslu, robotiky, chytrých budov a dalších kritických vestavěných systémových aplikací se předpokládá převzetí širšího spektra pracovních zátěží od nízkovýkonového monitorování v reálném čase až po vyspělé multimediální aplikace s grafickou prezentací na více obrazovkách u rozhraní člověk-stroj (HMI). Kromě splnění těchto širokých funkčních požadavků musejí být procesory těž schopny vyhovět přísným bezpečnostním standardům, požadavkům na snížení nákladů a půdorysu a optimalizovat rovnováhu mezi příkonem a výkonností.

Aby bylo možné těmto často protichůdným požadavkům vyhovět, vývojáři byli dosud nuceni buď obětovat funkční schopnosti, nebo zkomplikovat konstrukci a výrobu díky přídavným prvkům potřebným k zajištění podpory konkrétních požadavků mj. na grafiku a bezpečnost. Vývojáři tedy potřebují jednoduché řešení schopné podporovat širokou škálu produktů splňujících tyto požadavky pro široké spektrum kritických aplikací systémů s vestavěnými součástkami.

Tento článek stručně popisuje vývoj návrhu kritických systémů s vestavěnými součástkami. Následně ukáže, jakým způsobem lze vícejádrové aplikační procesory - speciálně navržené firmou Semiconductors pro podporu rychle expandujícího seznamu požadavků na širokou funkčnost a schopnost certifikovatelné bezpečnosti - využít k řešení vývojářských úloh.

Vývoj kritérií pro návrh systémů s vestavěnými součástkami

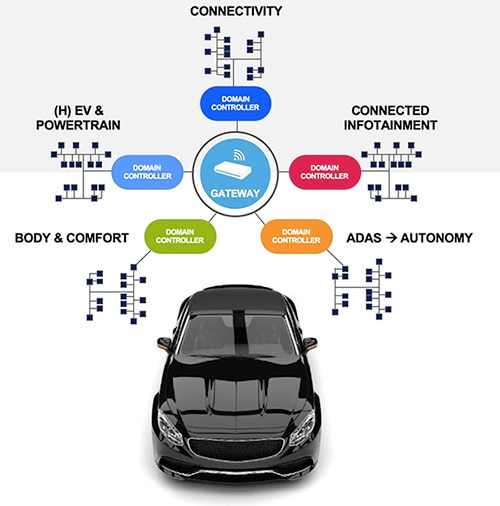

Tradiční úloha vestavěných součástek podporujících omezenou sadu systémových funkcí byla ve značné míře nahrazena poptávkou po součástkách poskytujících široké spektrum funkcí. Například potřeba vyspělých funkcí u rozhraní člověk-stroj (HMI) v chytrých nástrojích a zařízeních průmyslových aplikacích vyžaduje, aby procesory byly schopny dodávat optimalizovanou grafiku při současném splnění tradičnějších průmyslových požadavků v reálném čase. Podobně trend automobilových aplikací směřujících k hierarchickým architekturám zahrnujícím klastry funkční domény a hradla vyvolává potřebu procesorů schopných takovým požadavkům plně vyhovět (obrázek 1).

Obrázek 1: Trend směřující k vyšší hierarchii automobilových systémů vyvolal potřebu škálovatelných procesorových řešení s vyšší integrací. (Zdroj obrázku: NXP Semiconductors)

Obrázek 1: Trend směřující k vyšší hierarchii automobilových systémů vyvolal potřebu škálovatelných procesorových řešení s vyšší integrací. (Zdroj obrázku: NXP Semiconductors)

Poptávka po vyspělejších funkcích v jednotlivých funkčních doménách trvale posouvá práh výkonnosti a schopností integrace. Například nástup průhledových displejů vyžaduje řešení schopná řidičům trvale zajišťovat zobrazení kriticky důležitých grafických informací. Rostoucí potřeba zvýšeného povědomí řidičů společně s těmito displeji příští generace klade další požadavky na rozhraní kamer a vysoce výkonné provedení vyspělého rozpoznávacího softwaru schopného provádět detekci únavy.

S pokračujícím vývojem aplikací stoupá také naléhavost potřeby vysoce integrovaných, škálovatelných řešení, které musejí vyhovět čím dál rozmanitějším požadavkům při současné minimalizaci konstrukčního půdorysu, nákladů a složitosti. Pomocí skupiny i.MX 8 aplikačních procesorů od firmy NXP mohou vývojáři u kompatibilní platformy procesorů využít výkonnosti s celou řadu funkcí potřebných k podpoře široké škály aplikačních požadavků. Řada NPX i.MX 8X ve skupině i.MX 8 se zaměřuje rodící se potřeby bezpečnostně certifikovatelných procesorů požadovaných v aplikacích automobilů střední třídy a v průmyslu.

Vícejádrová architektura zvládá různé pracovní zátěže

Jedním z problémů, kterému čelí vývojáři při implementaci součástek pro automobilové a průmyslové aplikace, je samotný rozsah požadavků. V situacích, kdy by vývojáři mohli předpokládat řešení odezev v reálném čase nebo vysokých pracovních zátěží aplikačních procesů, poptávka po inteligentních subsystémech oba tyto významně odlišné typy výpočtů spojila. Vývojáři stále více potřebují řešení schopná poskytnout jak spolehlivou odezvu v reálné čase, tak i vysoce výkonné aplikace při současné podpoře funkčních bezpečnostních požadavků.

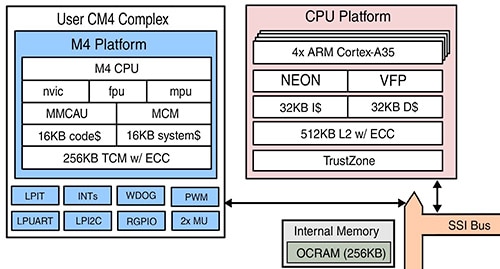

Procesory řady NXP i.MX 8X navržené se schopnostmi v reálném čase, vysokým výkonem zpracování a nízkým příkonem využívají všech předností architektury vyspělé vícejádrové centrální procesorové jednotky (CPU) ke zvládnutí různých výpočetních zátěží (obrázek 2).

Obrázek 2: Procesory NXP i.MX 8X řady používají vícejádrovou architekturu složenou z vestavěného procesoru Arm Cortex-M4 (CM4) a několika aplikačních procesorů Arm Cortex-A35, aby byla zajištěná podpora kombinovaných softwarových pracovních zátěží. (Zdroj obrázku: NXP Semiconductors)

Obrázek 2: Procesory NXP i.MX 8X řady používají vícejádrovou architekturu složenou z vestavěného procesoru Arm Cortex-M4 (CM4) a několika aplikačních procesorů Arm Cortex-A35, aby byla zajištěná podpora kombinovaných softwarových pracovních zátěží. (Zdroj obrázku: NXP Semiconductors)

Pro obecné úlohy zpracování v reálném čase zahrnují zařízení i.MX 8X procesor Arm Cortex-M4 (CM4) s jednotkou s plovoucí tečkou (FPU), ochrannou jednotku paměti (MPU), kryptografickou akcelerační jednotku s mapováním do paměti (MMCAU) a kombinovaný řídicí modul (MCM). Pro zajištění podpory externích periferií, například snímačů a aktuátorů, tento uživatelský celek CM4 kombinuje řadič přerušení s vnořeným vektorem (NVIC) s kompletní sadou rozhraní a modulů včetně periodického nízkovýkonového přerušovacího časovače (LPIT), pulzně-šířkové modulace (PWM) a dalších funkcí běžně vyžadovaných v automobilových a průmyslových aplikacích. Pár mezipamětí a úzce propojená paměť (TCM) s podporou opravného kódu chyb (ECC) pomáhají minimalizovat přístup do externích pamětí, urychlovat proces a odstraňovat paměťové chyby.

Pro zajištění rychlého chodu pracovních zátěží aplikací zahrnuje platforma CPU několik výkonově efektivních aplikačních procesorů (AP) Arm Cortex-A35 - dva AP v procesorech 8DualXPlus, například MIMX8UX6AVLFZAC, a čtyři AP v procesorech 8QuadXPlus, například MIMX8QX6AVLFZAC. Kromě vyhrazené instrukční (I$) a datové (D$) mezipaměti, zahrnuje platforma CPU sdílenou mezipaměť 512 kiloBytů (kByte) úrovně 2 (L2) s podporou opravného kódu chyb (ECC).

Jádra Arm Cortex-A35 v architektuře poskytují softwarovou kompatibilitu i škálovatelnou výkonnost s podporou 32bitové zpětné kompatibility a 64bitové výkonnosti. Pro další urychlení chodu výpočetně náročných algoritmů, například zpracování signálu a strojového učení, poskytují procesory Arm Cortex-A35 rozšíření architektury v podobě zpracování s vektorovou plovoucí tečkou (VFP) a technologie Arm Neon SIMD (jedna instrukce, více datových toků). Pro urychlení chodu softwaru pro zpracování snímků, počítačové vidění a strojové učení nabízí výpočetní knihovna Armfunkce optimalizované pro architektury procesoru Arm a grafické výpočetní jednotky (GPU) a knihovna open source Ne10 C poskytuje funkce optimalizované pro procesor Arm k provádění výpočetně náročných operací.

Speciální procesory odlehčují primárním jednotkám CPU

Kromě uživatelského celku CM4 a vícejádrové CPU platformy Arm Cortex-A35 poskytuje architektura přídavné speciální procesory pro multimediální aplikace. Společně s digitálním signálovým procesorem (DSP) na zpracování zvukových a hlasových kodeků architektura integruje grafickou výpočetní jednotku (GPU) a jednotku zpracování videa (VPU). Jednotka GPU v zařízení podporuje standardní grafické knihovny a urychluje operace pomocí čtyř samostatných, čtyřkomponentových vektorů s plovoucí tečkou (vec16), s 16 exekučními jednotkami a s vysoce výkonným, dvourozměrným bit blit procesorem. Jednotka VPU zpracovává populární video formáty s urychlením dekódování až na 4Kp30 (progresivní, 30 Hz) a kódování až na 1080p30. Speciální řídicí blok displeje v čipu může naopak odesílat grafický výstup až do tří nezávislých displejů.

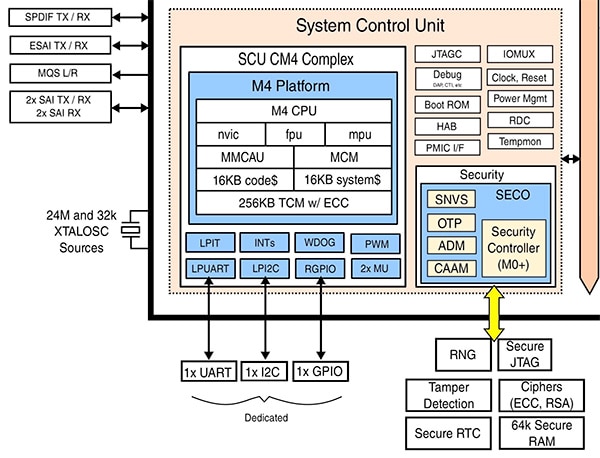

Pro další maximalizaci výkonu architektura MX 8X také integruje další procesorová jádra navržená na odlehčení primárních CPU platforem od přídavné pracovní zátěže, která typicky vzniká při spouštění služeb správy systému a bezpečnosti. Pro správu systému integruje systémová řídicí jednotka (SCU) architektury celek CM4, který se shoduje s uživatelským celkem CM4, zůstává však zcela vyhrazen pro operace jednotky SCU a není k dispozici vývojářům (obrázek 3).

Obrázek 3: Jednotka SCU používá vyhrazený subsystém Arm Cortex-M4 (CM4) na odlehčení hlavních procesorů od úloh správy systému, který je hluboko integrován v procesorech NXP i.MX 8X a není k dispozici pro vývojáře. (Zdroj obrázku: NXP Semiconductors)

Obrázek 3: Jednotka SCU používá vyhrazený subsystém Arm Cortex-M4 (CM4) na odlehčení hlavních procesorů od úloh správy systému, který je hluboko integrován v procesorech NXP i.MX 8X a není k dispozici pro vývojáře. (Zdroj obrázku: NXP Semiconductors)

Kromě správy výkonu, taktovacích signálů a dalších interních funkcí ovládá jednotka SCU také multiplexing vývodů a intenzitu buzení vstupně/výstupního kanálu (I/O) v normálním provozu. Uživatelský celek CM4 a aplikační procesory Arm Cortex-A35 AP de facto nemohou k těmto různým hardwarovým funkcím nízké úrovně přímo přistupovat. Úlohou jednotky je naopak tyto funkce oddělit tak, aby software běžící na uživatelském celku CM4 nebo aplikačních procesorech mohl jen zavolat funkce aplikačního programového rozhraní (API) firmwaru jednotky SCU za účelem spuštění funkcí například na vypnutí nepotřebných výkonových domén. Je-li taková doména například sdílená s jiným procesorem, jednotka SCU jednoduše potvrdí požadavek k vypnutí, ale bude tuto doménu dále udržovat pod napětím, dokud nevydá požadavek k vypnutí také druhý procesor.

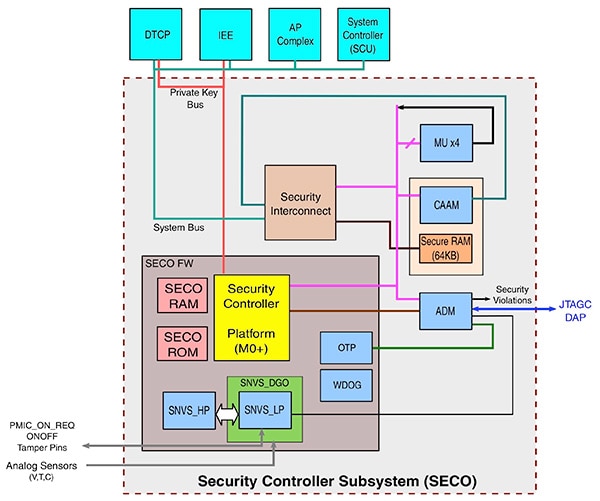

Na správu rozsáhlé podpory zabezpečení jednotky i.MX 8X vstupuje v subsystému ovladače zabezpečení (SECO) jednotky do hry další vyhrazený procesor. V subsystému SECO spouští integrovaný nízkovýkonový procesor Arm Cortex-M0+ firmware podporující hardwarové bezpečnostní funkce včetně soukromého přístupu na sběrnici pro bezpečnostní klíče, on-line programovatelné paměti (OTP) pro zabezpečené ukládání klíčů a zabezpečeného ukládání do energeticky nezávislých pamětí (SNVS) pro přídavná soukromá data nebo pomíjivé klíče (obrázek 4).

Obrázek 4: Uvnitř subsystému ovladače zabezpečení (SECO) procesoru NXP i.MX 8X řídí vyhrazený nízkovýkonový procesor Arm Cortex-M0+ bezpečnostní operace, pro které využívá sběrnici se soukromým klíčem a několik hardwarových modulů k zabezpečenému ukládání, kryptografické akceleraci a ověřenému přístupu k ladění. (Zdroj obrázku: NXP Semiconductors)

Obrázek 4: Uvnitř subsystému ovladače zabezpečení (SECO) procesoru NXP i.MX 8X řídí vyhrazený nízkovýkonový procesor Arm Cortex-M0+ bezpečnostní operace, pro které využívá sběrnici se soukromým klíčem a několik hardwarových modulů k zabezpečenému ukládání, kryptografické akceleraci a ověřenému přístupu k ladění. (Zdroj obrázku: NXP Semiconductors)

Kromě těchto základních bezpečnostních mechanismů koordinuje subsystém SECO bezpečnostní operace na detekci narušení a bezpečné ladění prostřednictvím svého modulu ověřeného ladění (ADM). Pro zajištění bezpečného chodu podporuje integrovaný bezpečnostní hardwarový kryptografický akcelerátor a zajišťovací modul (CAAM) kompletní soubor bezpečnostních algoritmů včetně symetrické a asymetrické kryptografie, hašovacích funkcí a generátoru náhodných čísel (RNG).

Při normálním provozu využívají procesorové jednotky zařízení včetně SCU, aplikačních procesorů a akcelerátoru digitální ochrany přepravovaného obsahu (DTCP) bezpečnostní propojení SECO k přístupu k funkcím CAAM prostřednictvím systémové sběrnice. Vyhrazený procesor Cortex-M0+ ovladače zabezpečení (SECO) nemůže přistupovat na systémovou sběrnici jinak, než prostřednictvím funkce přímého přístupu do paměti (DMA) kryptografického akcelerátoru a zajišťovacího modulu (CAAM). Využívá totiž chráněné interní připojení k přístupu k periferiím, zabezpečené paměti s náhodným přístupem (RAM) a paměti pouze pro čtení (ROM), jakož i vlastní speciální sběrnici se soukromým klíčem.

Společně s využitím akcelerátoru DTCP hraje tato sběrnice se soukromým klíčem zásadní úlohu v podpoře šifrování a dešifrování v reálném čase u procesoru i.MX 8X. Zabezpečovací procesor zde využívá svých prostředků k poskytování soukromých klíčů potřebných pro modul inline šifrovacího/dešifrovacích procesoru (IEE) zařízení, který provádí zabezpečené čtení z nebo zápis do šifrovaného úložiště, a to bez zapojení žádajícího procesoru, řadiče DMA nebo I/O zařízení.

Subsystém SECO postavený na technologii Arm TrustZone integrované v procesorech Cortex-A35 zařízení spolupracuje v průběhu zabezpečeného spouštění také s jednotkou SCU. Jednotka SCU v tomto procesu interpretuje nastavení spouštění, konfiguruje spouštěcí zdroje a zavádí spouštěcí bitové kopie do interní nebo externí paměti. Subsystém SECO následně pomocí svých kryptografických funkcí ověřuje podepsané bitové kopie pro firmware po jejich zavedení, avšak před spuštěním.

Zabezpečení kritických zobrazovacích a řídících funkcí

Ačkoli je schopnost účinného a bezpečného zpracování různých zátěží důležitá, pro klíčově významné aplikace, například v automobilových a průmyslových segmentech, je schopnost zabezpečení klíčových funkcí stejně zásadní. Skupina NXP's i.MX 8X spojuje své schopnosti zpracování s bezpečnostními certifikovatelnými funkcemi nutnými pro splnění těchto kritických požadavků.

Podpora bezpečnosti je u skupiny procesorů postavena na celé řadě úrovní počínaje procesní technologií plně ochuzeného křemíku na izolátoru (FD-SOI), která zvyšuje spolehlivost systému. Vzhledem k tomu, že bezpečnost systému závisí na robustních základech zabezpečení, může kombinace aplikačních procesorů s podporou technologie TrustZone, subsystému SECO a funkcí bezpečného spouštění zajistit důvěryhodné prostředí potřebné k zažehnání hrozeb bezpečnosti a zabezpečení.

Zároveň platí, že schopnost nezávislého zpracování časově kritických úloh pomocí uživatelského celku CM4 a odlehčení převedením kritických systémových úloh na subsystémy SCU a SECO pomáhá zajistit, aby klíčově významné aplikační funkce zůstaly dostupné i navzdory měnící se pracovní zátěži. Společnost NXP tuto koncepci vlastně rozšiřuje o podporu klíčově významných displejů prostřednictvím firemní technologie SafeAssure, která do zařízení i.MX 8X integruje cestu převzetí služeb při selhání pro hardware displejů podporujících úroveň integrity bezpečnosti silničních vozidel B (ASIL B). Díky technologii SafeAssure mají uživatelé automaticky k dispozici bitovou kopii převzetí služeb při selhání, pokud zařízení detekuje chybu datové integrity nebo jednotky GPU. Tato bitová kopie převzetí služeb při selhání běžící na pozadí zajišťuje, že kriticky důležité informace zůstanou dostupné i při selhání primárního displeje.

Podpora bezpečnostních aplikací sahá až k přístupu do paměti u systémů založených na procesorech i.MX 8X. V rámci podporovaných paměťových rozhraní poskytují zařízení i.MX 8X 8bitové opravné kódy chyb (ECC) pro paměti DDR3L (dvojnásobná datová rychlost 3, nízké napětí). Kromě kódů ECC v mezipaměti L2 (viz opět obrázek 2) podporuje tato funkce ECC pro paměti DDR3L také integritu průmyslové bezpečnosti úrovně 3 (SIL 3). Architektura procesorů i.MX 8X dále rozšiřuje podporu kódů ECC na externí úložná zařízení typu flash. Zde poskytuje integrovaný modul kodéru a dekodéru Bose, Ray-Chaudhuri, Hocquenghem (BCH) 62bitové kódy ECC schopné opravit 2 až 20 jednobitových chyb uvnitř bloku dat načteného z těchto úložných zařízení.

Zapínání aplikací založených na procesorech i.MX 8X

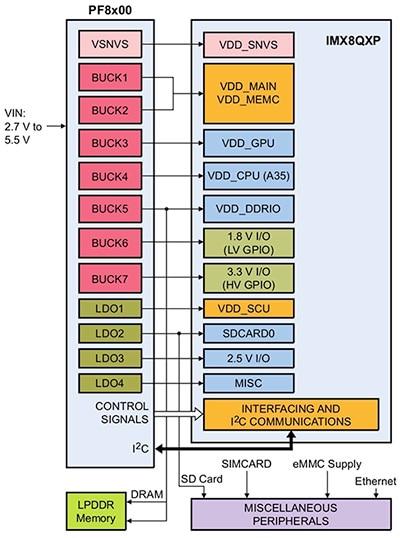

Stejně jako u libovolného procesoru této třídy platí, že implementace konstrukce založené na procesorech i.MX 8X vyžaduje důsledné dodržování přísných požadavků na výkon včetně kritických spouštěcích sekvencí. Zapnutí zařízení i.MX 8X vyžaduje postupné nebo současné přivedení energie do čtyřech různých napájecích skupin od subsystému SVNS přes SCU, I/O a paměťová rozhraní až po zbytek zařízení. Vývojáři mohou tento požadavek naplnit prostým použitím zařízení s integrovaným obvodem řízením spotřeby energie (PMIC) PF8x00 od společnosti NXP, která poskytují kompletní sadu napěťových sběrnic a řídicích signálů potřebných k podpoře procesorů i.MX 8X, externí paměti a typických systémových periferií (obrázek 5).

Obrázek 5: Obvody NXP PMIC PF8x00 poskytují kompletní sadu napěťových sběrnic a řídicích signálů potřebných k napájení procesorů i.MX 8X. (Zdroj obrázku: NXP Semiconductors)

Obrázek 5: Obvody NXP PMIC PF8x00 poskytují kompletní sadu napěťových sběrnic a řídicích signálů potřebných k napájení procesorů i.MX 8X. (Zdroj obrázku: NXP Semiconductors)

Při implementaci vlastních konstrukcí založených na procesorech i.MX 8X mohou vývojáři využít obvod NXP MC33PF8100CCES PMIC přeprogramovaný pro použití s procesory 8QuadXPlus, například MIMX8QX6AVLFZAC. Jiné varianty PF8x00, například MC33PF8100A0ES a MC33PF8200A0ES podporují procesory i.MX 8X, avšak nejsou přeprogramované.

Pro bezpečnostní aplikace integrují zařízení řady PF8200, například MC33PF8200A0ES, funkce navržené na podporu systémů ASIL B. Společně s několika interními monitorovacími funkcemi včetně monitorování výstupního napětí pomocí speciální reference typu bandgap zahrnují IO pro řízení napájení (PMIC) v zařízení PF8200 výstupní vývod zabezpečený proti selhání určený k udržení systému v bezpečném stavu během spouštění nebo při výpadku napájení. Vestavěná analogová samotestovací rutina (ABIST) dále testuje všechny monitorovací funkce napětí, zatímco samotestovací rutina ověřuje funkčnost ostatních zařízení.

Ačkoli mohou IO pro řízení napájení (PMIC) v zařízení PF8x00 zjednodušit hardwarovou konstrukci systémů založených na procesorech i.MX 8X, někteří vývojáři budou pravděpodobně potřebovat ihned začít vyhodnocovat zařízení i.MX 8X a rychle prototypovat aplikace založené na procesorech i.MX 8X. Multisenzorická aktivační sada (MEK)MCIMX8QXP-CPU i.MX 8X od společnosti NXP poskytuje platformu připravenou pro vývoj zahrnující procesor NXP i.MX 8QuadXPlus, obvod PMIC NXP F8100, 3gigabytovou (GB) paměť RAM, vestavěnou 32GB paměť multimediálního ovladače (eMMC) a 64megabytovu (MB) paměť flash. Společně s displejem, kamerou a zvukovými rozhraními obsahuje deska MEK sadu snímačů typicky používaných v automobilových nebo průmyslových aplikacích. Pro přídavnou konektivitu, zvuk a rozšiřující možnosti mohou vývojáři přidat též volitelnou základní desku MCIMX8-8X-BB od společnosti NXP.

Závěr

S rostoucím počtem aplikací, například pro automobily, průmysl, chytré budovy a rozhraní člověk-stroj (HMI), se pracovní zátěže procesů rozšířily jak o tradiční I/O zpracování v reálném čase, tak i o rodící se zpracování na aplikační úrovni s multimediální grafikou. Ačkoli pro každý typ pracovní zátěže existují různé konstrukční varianty, jen málo dostupných řešení vyhovuje rostoucím potřebám energeticky účinných řešení s vysokou výkonností schopných splnit požadavky na bezpečnostně certifikovatelné konstrukce v automobilových a průmyslových aplikacích.

Jak je ukázáno, s využitím skupiny vícejádrových procesorů od společnosti XP Semiconductors mohou vývojáři účinněji implementovat konstrukce schopné vyhovět těmto rozmanitým požadavkům a snadno je škálovat tak, aby reagovaly na rodící se potřeby vysoké výkonnosti.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.