Jak používat SoC FPGA pro zabezpečené a propojené systémy pevného reálného času

Contributed By DigiKey's North American Editors

2023-02-16

Důležitými nástroji pro konstruktéry jsou programovatelná hradlová pole („field programmable gate array“, FPGA), subsystémy mikrokontroléru („microcontroller unit“, MCU) RISC-V podporující Linux, pokročilé architektury paměti a vysoce výkonná komunikační rozhraní. To platí zejména pro konstruktéry zabezpečených propojených systémů, systémů kritických z hlediska bezpečnosti a širokou škálu deterministických systémů pevného reálného času, jako je umělá inteligence („artificial intelligence“, AI) a strojové učení („machine learning“, ML).

Integrace těchto různorodých prvků do zabezpečeného, propojeného a deterministického systému však může být obtížnou a časově náročnou činností, stejně jako rozložení vysokorychlostních propojení pro různé prvky systému. Pro vysokorychlostní konektivitu musí konstruktéři zahrnout jednotku správy paměti, jednotku ochrany paměti, možnost zabezpečeného spouštění a gigabitové transceivery. Návrh bude vyžadovat aktivní a statické řízení napájení a řízení náběhových proudů. Některé návrhy budou vyžadovat provoz v rozšířeném komerčním rozsahu teplot 0 °C až +100 °C teploty přechodu (TJ), zatímco systémy v průmyslovém prostředí budou muset pracovat s teplotou TJ od −40 °C do +100 °C.

Při řešení těchto a dalších problémů mohou konstruktéři využít zařízení systému na čipu („system-on-chip“, SoC) FPGA, která kombinují nízkou spotřebu energie, tepelnou účinnost a zabezpečení na obranné úrovni pro chytré, propojené a deterministické systémy.

V tomto článku je shrnuta architektura takového SoC FPGA a to, jak podporuje efektivní návrh propojených a deterministických systémů. Poté je zde stručně představen srovnávací test EEMBC CoreMark-Pro výpočetního výkonu versus spotřeba energie spolu s pohledem na výkon reprezentativního SoC FPGA ve srovnávacím testu. Článek pojednává o tom, jak je v těchto SoC FPGA řešeno zabezpečení, a podrobně popisuje příklady SoC FPGA od společnosti Microchip Technology spolu s vývojovou platformou k urychlení procesu návrhu. Na závěr je uveden stručný seznam rozšiřujících desek od společnosti MikroElektronika, které lze použít k implementaci řady komunikačních rozhraní stejně jako k funkci lokalizace globálního navigačního satelitního systému („global navigation satellite system“, GNSS).

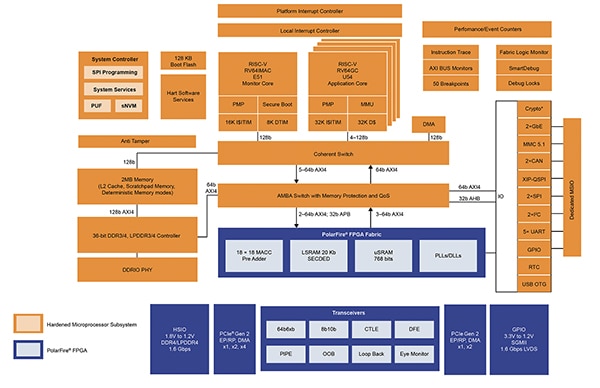

SoC sestavené se strukturou FPGA

„Čipem“ pro tento SoC je struktura FPGA, která obsahuje systémové prvky od FPGA po subsystém MCU RISC-V, který je postaven s posílenou logikou FPGA. Subsystém MCU zahrnuje čtyřjádrový cluster MCU RISC-V, monitorovací jádro RISC-V, systémový řadič a deterministický paměťový subsystém úrovně 2 („Level 2“, L2). FPGA v těchto SoC obsahuje až 460 K logických prvků, transceivery až 12,7 Gb/s a další vstupně/výstupní („input/output“, I/O) bloky, včetně univerzálního I/O rozhraní („general purpose input/output“, GPIO) a rozhraní PCIe („Peripheral Component Interconnect Express“) 2. Celková architektura je navržena s ohledem na spolehlivost. Obsahuje korekci jedné chyby a detekci dvojí chyby („single-error correction and double-error detection“, SECDED) na všech pamětech, diferenciální analýzu napájení („differential power analysis“, DPA), fyzickou ochranu paměti a 128 kbitů spouštěcí paměti flash (obrázek 1).

Obrázek 1: Všechny prvky v tomto SoC FPGA, včetně subsystémů RISC-V, jsou implementovány na struktuře FPGA. (Zdroj obrázku: společnost Microchip Technology)

Obrázek 1: Všechny prvky v tomto SoC FPGA, včetně subsystémů RISC-V, jsou implementovány na struktuře FPGA. (Zdroj obrázku: společnost Microchip Technology)

Společnost Microchip nabízí svůj ekosystém Mi-V (vyslovováno anglicky jako „my five“) s nástroji a prostředky návrhu třetích stran pro podporu implementace systémů RISC-V. Systém je navržen tak, aby urychlil přijetí architektury instrukční sady („instruction set architecture“, ISA) RISC-V pro posílená jádra RISC-V a pro softcore RISC-V. Prvky ekosystému Mi-V zahrnují přístup k následujícímu:

- Licence duševního vlastnictví („Intellectual property“, IP)

- Hardware

- Operační systémy a middleware

- Debuggery, kompilátory a návrhové služby

Posílené MCU RISC-V v SoC FPGA obsahují několik možností ladění, jako je pasivní běhové konfigurovatelné pokročilé rozšiřitelné rozhraní („advanced extensible interface“, AXI) a sledování instrukcí. Rozhraní AXI umožňuje konstruktérům monitorovat data, která se zapisují nebo čtou z různých pamětí, a vědět, kdy jsou zapisována nebo čtena.

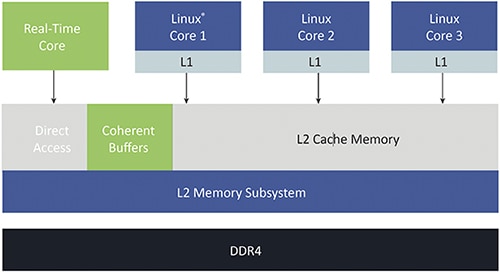

Subsystém MCU RISC-V využívá pětistupňovou pipeline stylu in-order s šířkou 1-issue. Není zranitelný vůči zneužitím Spectre nebo Meltdown, která mohou postihnout architektury out-of-order. Všech pět MCU je koherentních s paměťovým subsystémem a podporuje kombinaci deterministických systémů reálného času v režimu asymetrického multi-processingu („asymmetric multi-processing“, AMP) a Linuxu. Mezi možnosti subsystému RISC-V patří (obrázek 2):

- Spuštění systému Linux a operací pevného reálného času

- Konfigurace L1 a L2 jako deterministické paměti

- Paměťový subsystém DDR4

- Zakázání/povolení prediktorů větvení

- Provoz pipeline in-order

Obrázek 2: Subsystém RISC-V obsahuje několik procesorových a paměťových prvků. (Zdroj obrázku: společnost Microchip Technology)

Obrázek 2: Subsystém RISC-V obsahuje několik procesorových a paměťových prvků. (Zdroj obrázku: společnost Microchip Technology)

Více zpracování s méně energie

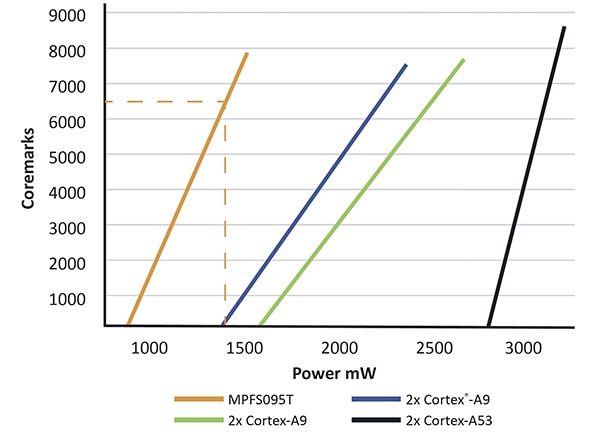

Kromě výhod systémových operací, včetně podpory zpracovávání v pevném reálném čase, jsou tyto SoC FPGA vysoce energeticky účinné. Srovnávací test EEMBC CoreMark-PRO je průmyslový standard pro porovnávání účinnosti a výkonu MCU ve vestavěných systémech. Test byl navržen speciálně k porovnávání výkonu hardwaru a k nahrazení srovnávacího testu Dhrystone.

Pracovní zátěže CoreMark-PRO zahrnují rozmanité výkonnostní charakteristiky, paralelismus na úrovni instrukcí a využití paměti založené na čtyřech pracovních zátěžích s plovoucí desetinnou čárkou a pěti běžných celočíselných pracovních zátěžích. Pracovní zátěže s plovoucí desetinnou čárkou zahrnují rutinu lineární algebry odvozenou ze srovnávacího testu LINPACK, rychlou Fourierovu transformaci, algoritmus neuronové sítě pro vyhodnocování vzorů a vylepšenou verzi srovnávacího testu smyček Livermore. Základ celočíselných pracovních zátěží tvoří komprese JPEG, analyzátor XML, komprese ZIP a 256bitový zabezpečený hashovací algoritmus („secure hash algorithm“, SHA-256).

Modely MPFSO95T těchto SoC FPGA, jako např. MPFS095TL-FCSG536E, mohou dodat hodnotu až 6 500 Coremark při 1,3 wattu (obrázek 3).

Obrázek 3: SoC FPGA MPFS095T (oranžová čára) poskytuje hodnotu 6 500 Coremark při 1,3 wattu. (Zdroj obrázku: společnost Microchip Technology)

Obrázek 3: SoC FPGA MPFS095T (oranžová čára) poskytuje hodnotu 6 500 Coremark při 1,3 wattu. (Zdroj obrázku: společnost Microchip Technology)

Aspekty zabezpečení

Aplikace kritické z hlediska bezpečnosti a aplikace pevného reálného času pro tyto SoC FPGA vyžadují kromě vysoké energetické účinnosti a výkonných možností zpracování také silné zabezpečení. Mezi základní funkce zabezpečení těchto SoC FPGA patří programování bitstreamu odolné proti diferenciální analýze výkonu (DPA), generátor pravých náhodných čísel („true random number generator“, TRNG) a fyzicky neklonovatelná funkce („physically unclonable function“, PUF). SoC FPGA zahrnují také standardní a uživatelem definované zabezpečené spouštění, fyzickou ochranu paměti, která poskytuje omezení přístupu k paměti související se stavem oprávnění počítače, včetně režimů počítače, supervizora nebo uživatele, a imunitu proti útokům Meltdown a Spectre.

Zabezpečení začíná bezpečným řízením zásobovacího řetězce, včetně použití hardwarových bezpečnostních modulů („hardware security module“, HSM) během testování a pouzdření desky (waferu). K zajištění zásobovacího řetězce přispívá použití 768bajtového digitálně podepsaného certifikátu x.509 FPGA zabudovaného do jednotlivých SoC FPGA.

Tyto SoC FPGA obsahují mnoho detektorů neoprávněné manipulace na čipu, které zajišťují bezpečný a spolehlivý provoz. Pokud je zjištěna neoprávněná manipulace, dojde k vydání příznaku neoprávněné manipulace, který systému umožňuje reagovat podle potřeby. Některé z dostupných detektorů neoprávněné manipulace zahrnují:

- Monitory napětí

- Snímače teploty

- Detektory poruch taktu a detektory taktovací frekvence

- Aktivní detektor JTAG

- Aktivní detektor sítě

Zabezpečení je dále zajištěno pomocí protiopatření proti útoku korelační odběrovou analýzou („correlation power attack“, CPA) symetrických blokových cifer 256bitového standardu pokročilého šifrování („advanced encryption standard“, AES-256), integrovaných funkcí kryptografického otisku pro zajištění integrity dat, integrované PUF pro úložiště klíčů a možností zeroizování pro strukturu FPGA a všechny paměti na čipu.

Příklady SoC FPGA

Společnost Microchip Technology tyto možnosti a technologie kombinuje do svých SoC FPGA PolarFire s několika stupni rychlostí, teplotními jmenovitými hodnotami a různými velikostmi pouzdra, aby podpořila potřeby konstruktérů pro širokou škálu řešení s logickými prvky mezi 25 K a 460 K. K dispozici jsou čtyři teplotní stupně (všechny se vztahují k TJ): rozšířený komerční rozsah 0 °C až +100 °C, průmyslový rozsah −40 °C až +100 °C, rozsah pro automobilový průmysl −40 °C až +125 °C a vojenský rozsah −55 °C až +125 °C.

Konstruktéři si mohou vybrat mezi zařízeními se standardní rychlostí nebo zařízeními se stupněm rychlosti −1, která jsou o 15 % rychlejší. Tyto SoC FPGA mohou být provozovány s nejnižším výkonem při 1,0 V nebo s vyšším výkonem při 1,05 V. K dispozici jsou v řadě velikostí pouzdra, včetně 11 × 11 mm, 16 × 16 mm a 19 × 19 mm.

Pro aplikace, které vyžadují rozšířený komerční teplotní provoz, provoz se standardní rychlostí a 254 K logických prvků v pouzdře 19 × 19 mm, mohou konstruktéři využít model MPFS250T-FCVG484EES. Pro jednodušší řešení, která potřebují 23 K logických prvků, mohou konstruktéři využít model MPFS025T-FCVG484E, také s rozšířeným komerčním teplotním provozem a standardní rychlostí v pouzdru 19 × 19 mm. Model MPFS250T-1FCSG536T2 s 254 K logickými prvky je určen pro vysoce výkonné automobilové systémy a má rozsah provozních teplot −40 °C až 125 °C a rychlostní stupeň −1 pro o 15 % rychlejší hodiny, je v kompaktním pouzdru 16 × 16 mm s 536 kuličkami s roztečí 0,5 mm (obrázek 4).

Obrázek 4: Model MPFS250T-1FCSG536T2 s teplotou pro automobilový průmysl se dodává v pouzdru 16 × 16 mm s počtem kuliček 536 a roztečí 0,5 mm. (Zdroj obrázku: společnost Microchip Technology)

Obrázek 4: Model MPFS250T-1FCSG536T2 s teplotou pro automobilový průmysl se dodává v pouzdru 16 × 16 mm s počtem kuliček 536 a roztečí 0,5 mm. (Zdroj obrázku: společnost Microchip Technology)

Vývojová platforma SoC FPGA

Pro urychlení návrhu systémů s SoC FPGA PolarFire nabízí společnost Microchip sadu PolarFire SoC Icicle MPFS-ICICLE-SADA-ES, která umožňuje prozkoumávání pětijádrového mikroprocesorového subsystému RISC-V s podporou Linuxu s nízkou spotřebou energie a v reálném čase. Sada obsahuje bezplatnou licenci Libero Silver, která je potřebná pro vyhodnocování návrhů. Podporuje funkce programování a ladění v jediném jazyce.

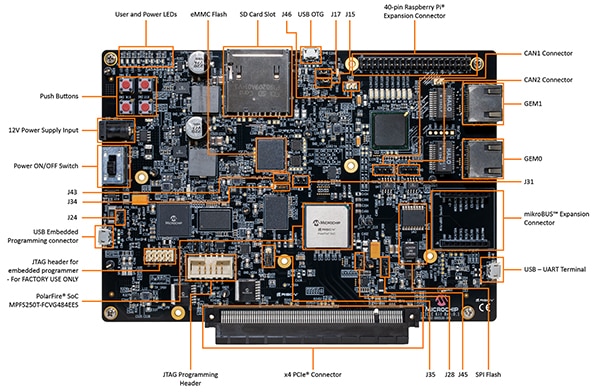

Tyto SoC FPGA jsou podporovány sadou pro vývoj softwaru („software development kit“, SDK) akcelerátoru VectorBlox, která umožňuje aplikace AI/ML s nízkou spotřebou energie a v malém tvarovém faktoru. Důraz je kladen na zjednodušení procesu návrhu do té míry, že konstruktéři nemusí mít s návrhem FPGA předchozí zkušenosti. Sada SDK akcelerátoru VectorBlox umožňuje vývojářům programovat energeticky úsporné neuronové sítě pomocí jazyka C/C++. Sada Icicle má řadu funkcí, které poskytují komplexní vývojové prostředí, včetně systému senzorů napájení ve více vedeních pro monitorování různých domén napájení, kořenového portu PCIe a vestavěných pamětí – včetně LPDDR4, QSPI a eMMC Flash – pro provoz Linuxu a Raspberry Pi a rozšiřující porty mikroBUS pro řadu možností kabelového a bezdrátového připojení plus funkční rozšíření, jako je schopnost lokalizace GNSS (obrázek 5).

Obrázek 5: Toto komplexní vývojové prostředí SoC FPGA obsahuje konektory pro rozšiřující desky Raspberry Pi (vpravo nahoře) a mikroBUS (níže při pravé straně). (Zdroj obrázku: společnost Microchip Technology)

Obrázek 5: Toto komplexní vývojové prostředí SoC FPGA obsahuje konektory pro rozšiřující desky Raspberry Pi (vpravo nahoře) a mikroBUS (níže při pravé straně). (Zdroj obrázku: společnost Microchip Technology)

Rozšiřující desky

Mezi několik příkladů rozšiřujících desek mikroBUS patří:

MIKROE-986 pro přidání konektivity sběrnice CAN pomocí sériového periferního rozhraní („serial peripheral interface“, SPI).

MIKROE-1582 pro propojení mezi MCU a sběrnicí RS-232.

MIKROE-989 pro spojení s komunikační sběrnicí RS422/485.

MIKROE-3144 podporující technologie LTE Cat M1 a NB1 umožňující spolehlivou a jednoduchou konektivitu se zařízeními 3GPP IoT.

MIKROE-2670 umožňující funkci GNSS se současným příjmem konstelací GPS a Galileo plus buď BeiDou, nebo GLONASS, což má za následek vysokou přesnost polohy v situacích se slabým signálem nebo rušením v městských údolích.

Závěr

Při vývoji propojených deterministických systémů pevného reálného času kritických z hlediska bezpečnosti mohou konstruktéři využít SoC FPGA. SoC FPGA poskytují širokou škálu systémových prvků, včetně struktury FPGA, subsystému MCU RISC-V s vysoce výkonnými pamětmi, vysokorychlostních komunikačních rozhraní a četných bezpečnostních funkcí. Jako pomoc konstruktérům se začátkem jsou k dispozici vývojové desky a prostředí, které obsahují všechny potřebné prvky, včetně rozšiřujících desek, které lze použít k implementaci široké škály komunikačních a lokalizačních funkcí.

Doporučeno k přečtení

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.